2D 中值滤波算法实现

judy 在 周一, 07/03/2023 - 09:40 提交

使用高级综合HLS,开发 2D 中值滤波器算法 (HLS)

在FPGA的设计中的,内部的FIFO和RAM是两种非常常见的存储单元

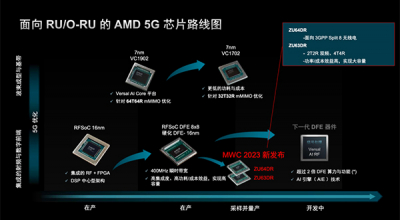

通信业已经进入5G时代。运营商投资建网、设备商提供各类5G设备和解决方案

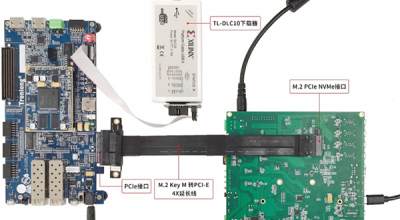

本文介绍基于瑞芯微RK3568J与Xilinx Artix-7的PCIe高速通信案例

FreeRTOS也可以说是standalone的程序。因此可以方便的把AMD Xilinx的standalone的例子

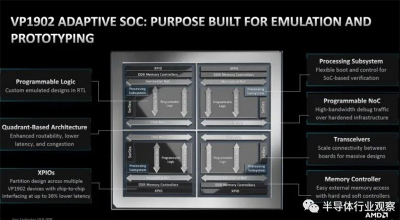

1902增加了Versal功能,并采用了小芯片设计,使FPGA的关键性能增加了一倍以上

新型 AMD Versal Premium VP1902 有效地将可模拟多达 1850 万个逻辑单元的门数增加了一倍

第三代AMD EPYC处理器采用7nm工艺,可以提供至高64个计算核心

Sirius Wireless 的 Wi-Fi6/BT 射频 IP 验证系统基于思尔芯芯神瞳 S7-9P逻辑系统构建

本文继续讲解时序约束的第四大步骤——时序例外