Vivado SDK生成、使用静态库

matt z 在 周四, 03/23/2023 - 10:09 提交

在Xilinx/Vivado环境下,针对Non-OS环境,可以使用静态库;针对Linux环境,可以使用静态库和动态库

在Xilinx/Vivado环境下,针对Non-OS环境,可以使用静态库;针对Linux环境,可以使用静态库和动态库

本文将探讨如何在 Vitis™ 中使用 Git 集成以及如何使用团队操作来共享 Vitis 工程

dBV(V大写),dBu(u小写),是模拟音频时代最常用到的两个单位。

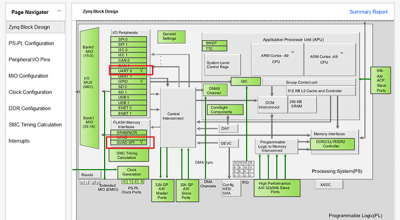

本文将无DDR固化的情况进一步进行介绍,讲解如何修改FSBL实现ZYNQ的程序固化

Vitis软件平台由适用于交互式工程开发的集成设计环境和适用于脚本化或手动应用开发的命令行工具组成

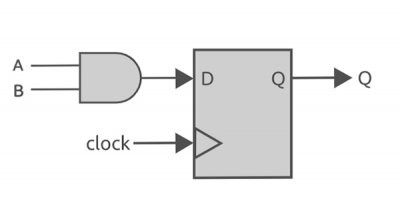

本文将讲述如何使用Verilog 编写一个基础的测试脚本(testbench)。

在vivado-Tool-setting-project-setting-synthesis路径下,设置 -mode out_of_context