直击慕尼黑上海电子展,ALINX 以 FPGA 助推企业客户产品研发冲刺

judy 在 周五, 04/18/2025 - 10:58 提交

芯驿电子携全线产品矩阵和行业应用解决方案亮相,从硬件平台到配套 IP、从通信链路到图像处理,全面展现 FPGA 在智能化时代的落地潜力。

芯驿电子携全线产品矩阵和行业应用解决方案亮相,从硬件平台到配套 IP、从通信链路到图像处理,全面展现 FPGA 在智能化时代的落地潜力。

在可编程逻辑器件领域,基于SRAM的FPGA经常被误解。这些FPGA具有极高的灵活性和可重新配置特性,是从消费电子到航空航天等各类应用的理想选择

Altera 大学项目旨在帮助教授们将基于现代 FPGA 工具的最新设计融入教学,从而为学生提供有益于未来职业发展的实践经验和实战技能。

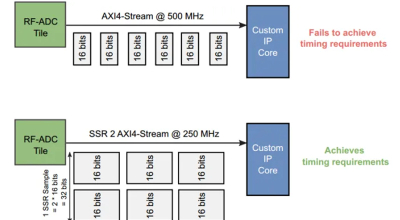

当使用RFSoC进行原型设计时,通常需要外部无线电组件。例如,可能需要天线来改善信号采集,或者需要外部滤波器来抑制频谱混叠

在FPGA设计领域,西安智多晶微电子推出的LPC_Controller IP正逐渐崭露头角,为工程师们提供了强大的工具,助力他们在数据传输领域大展身手

HBM4 支持 4 高、8 高、12 高和 16 高 DRAM 堆栈配置,具有 24 Gb 或 32 Gb 芯片密度,可提供 64GB(32 Gb 16 高)的更高立方体密度

本白皮书探讨了如何基于 Kahn 处理网络( KPN )定义 AI 引擎图形编程模型。KPN 模型有助于实现数据流并行化,进而提高系统的整体性能

本文将从多方面深入分析该交易带来的潜在收益与风险,以及Altera未来面临的机遇和挑战。

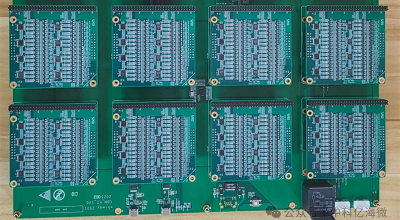

基于中科亿海微FPGA的智能超表面通信控制板主要用于控制入射到智能超表面上可重构PIN二极管元件的相位和幅度,从而重新配置入射无线电信号的传播并实现“智能无线电环境”

在机器人技术爆发式发展的今天,低功耗、安全性和实时处理能力已成为三大核心挑战。Microchip最新推出的PolarFire® FPGA系列,正是为解决这些痛点而生!