MMU的设计

judy 在 周五, 09/09/2022 - 15:39 提交

什么是MMU?MMU是Memory Management Unit的缩写,这原本是软件内存管理方面的一个概念

什么是MMU?MMU是Memory Management Unit的缩写,这原本是软件内存管理方面的一个概念

Vitis HLS是Vitis AI重要组成部分,所以我们将重点介绍Vitis HLS。

数字时代蓬勃发展,算力已成为重要的生产力,它像水、电一样,是当今社会的核心资源。

本视频主要演示 WeGo 如何通过在框架内提供分区、量化及编译自动化,帮助提供从训练到部署的增强用户体验

无论是FPGA还是ASIC的开发者,都或多或少地做过代码检视(code review)。

在异步跨时钟域场合,对于控制信号(通常位宽为1bit)常使用双触发器的方式完成跨时钟域操作

Ultra96-V2 是基于 Linaro 96Boards Consumer Edition(CE)规范、基于 Arm 的 Xilinx Zynq UltraScale +™MPSoC 开发板。

本文将探讨如何以 Zynq UltraScale 器件上的 IP 核为目标,使用 Python 来创建一些强大的应用和实用工具。

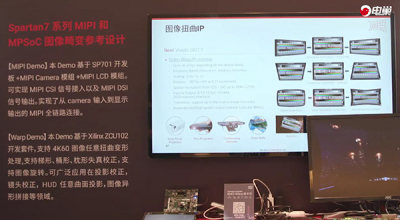

本 Demo 基于 SP701 开发板 +MIPI Camera 模组 +MIPI LCD 模组

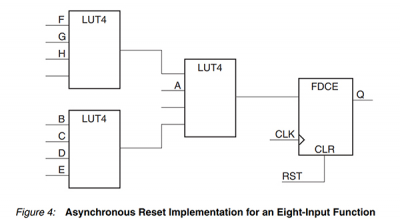

实现FPGA 设计最大性能化的一个重要因素是正确的RTL 编码设计。