在 Vivado 中使用 HLS 创建的IP

judy 在 周四, 09/22/2022 - 09:44 提交

在本实践中,我们将实际实现 HLS 组件作为 FPGA 设计的一部分

在本实践中,我们将实际实现 HLS 组件作为 FPGA 设计的一部分

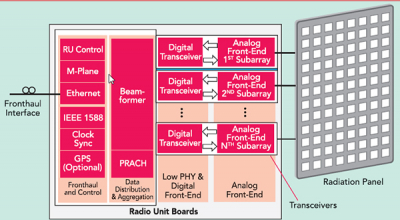

本文提供了关于O-RAN架构的教程,以及规范RU、DU和CU之间接口的方法,以实现互操作性

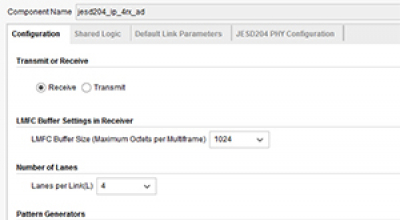

Xilinx JESD204B IP testbench解析

Vitis AI Library 是一组高层次库和 API,专为利用深度学习处理单元 (DPU) 来高效执行 AI 推断而构建

前面介绍了CityHash32中前3种场景下的算法实现,这里继续介绍最后一种,也是最复杂的一种

本篇设计咨询涵盖了 Versal GTM 复位不稳定问题

AMD已经确认第一批Phoenix Point处理器样品正在实验室当中运行,这些处理器内置了赛灵思AI加速引擎。

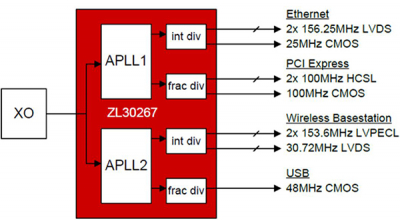

随着FPGA的功能越来越强大,并且有SOC等异构的架构不断演进,硬件设计也有更多的时钟要求

Hash是FPGA设计中非常常见的一个功能。它是将一个Mbyte长度的数据通过hash计算变成一个Nbyte长度的数据

KR260首先从QSPI加载BOOT.BIN启动U-BOOT,U-BOOT再从SD(TF)卡的第1个分区(sda1)启动Linux内核