时序分析基本概念(一)——建立时间

judy 在 周日, 10/09/2022 - 10:01 提交

以上升沿锁存为例,建立时间(Tsu)是指在时钟翻转之前输入的数据D必须保持稳定的时间。

以上升沿锁存为例,建立时间(Tsu)是指在时钟翻转之前输入的数据D必须保持稳定的时间。

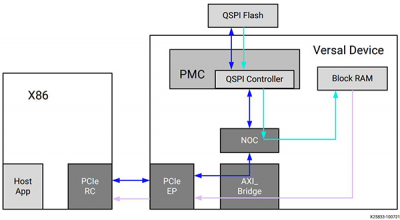

本应用说明提供了一个使用外部CPU编程QSPI闪存的参考设计。

本文就跟大家分享如何使用Xilinx AXI VIP对自己的设计搭建仿真验证环境的方法。

分享如何使用Xilinx ZYNQ Ultrascale+ MPSoC的PS端原生DP接口实现LIVE模式输出3860*2140,30Hz视频。

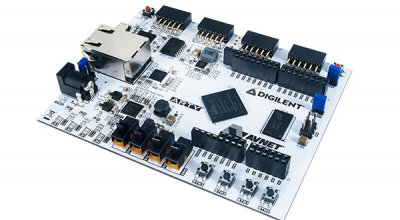

本设计使用 Zynq7020 芯片采用自制的 双 hdmi 拓展板,结合 FPGA 与 ARM 的优势。在硬件层面分为加密端和解密端

AMD首席执行官 Lisa Su 博士近来在接受挪威主权财富基金采访时分享了她对公司当前业绩、整个行业以及员工生产力重要性的看法

使用KR260 PetaLinux 2022.1 BSP创建工程后,使用产生的wic文件烧录tf卡,Linux启动报告错误

来自两位开发者的新工作流工具,使得一枚普通的 FPGA、能够实现较传统 x86 处理器更惊人的效率提升

对于 ZCU111 rev 1.0 EVB 而言,如果 VADJ 值在 SCUI GUI 中配置为 1.8V(或保留默认值)

Linux 下应用程序要通过设备驱动程序来访问外设。这就需要在设备树中添加设备,并且编写设备驱动程序。