基于点云的 3D 对象检测系统

judy 在 周二, 06/28/2022 - 10:00 提交

该项目将借助 KV260 上的 PYNQ -DPU 覆盖,从而能够使我们在 LiDAR 点云上进行 3D 对象检测比以往任何时候都更加高效!

该项目将借助 KV260 上的 PYNQ -DPU 覆盖,从而能够使我们在 LiDAR 点云上进行 3D 对象检测比以往任何时候都更加高效!

CLB实际上是四种基本元素的集合----查找表LUT,进位链CARRY4,多路选择器Multiplexer以及存储单元FF。

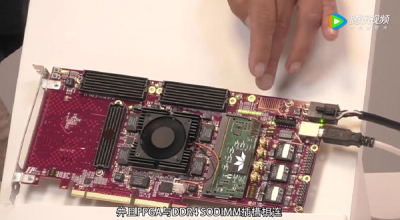

观看这个短视频,了解如何连接Teledyne e2v耐辐射DDR4存储器与AMD XILINX Kintex Ultrascale FPGA KU115。

这个简单的Demo是介绍如何用ChipScopy创建并运行link sweep。

在过去的几十年里,数据处理和存储系统可以用最好的组件来构建,而市场可以在计算、网络和存储每一类别中支持多个竞争性技术供应商。

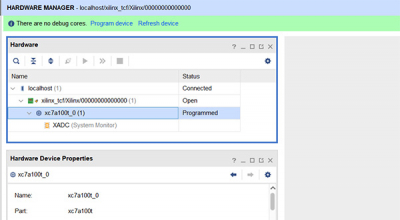

Xilinx Platform Cable USB II无论是官方的DLC10,还是第三方的DLC9均无法 识别,表现为以下几种

在这个短视频中,您将学习如何设置DDR4 控制器IP,以连接Teledyne e2v DDR4产品和Xilinx的可编程逻辑器件。

在 Vitis 应用加速流程中,在可编程逻辑中实现和最优化 C/C++ 语言代码以及实现低时延和高吞吐量所需的大部分代码修改操作均可通过 Vitis HLS 工具来自动执行。

FPGA底层的CARRY4本质上就是用来实现最基本的加、减法运算的,在了解CARRY4之前,我们需要对1bit以及多bit的二进制加法及其FPGA实现做一个了解。

今天给大家介绍一下FPGA上部署深度学习的算法模型的方法以及平台。希望通过介绍,算法工程师在FPGA的落地上能“稍微”缓和一些,小白不再那么迷茫。