FPGA时钟篇(一) 7系列的时钟结构

judy 在 周三, 04/06/2022 - 09:52 提交

从本篇文章开始,我们来介绍下Xilinx FPGA的时钟结构、资源、用法,首先从7系列的FPGA开始,因为7系列的FPGA结构跟前面的有很大不同,而且前面那些FPGA用的也越来越少了。

从本篇文章开始,我们来介绍下Xilinx FPGA的时钟结构、资源、用法,首先从7系列的FPGA开始,因为7系列的FPGA结构跟前面的有很大不同,而且前面那些FPGA用的也越来越少了。

本文通参考MATLAB的RF仿真工具,展示如何在发射机中使用数字预失真(DPD)来抵消功率放大器中非线性的影响。

在2月份完成收购FPGA公司Xilinx后,AMD是否与高通、Nvidia一样,有明确的汽车战略吗?是否会承诺一个5-10年的计划,真正成为汽车芯片市场的重要玩家?

本文写了三个示例,展示了三种综合脚本的写法,供大家可以参考。

在Vivado或其他综合工具(如Synplify)上,综合阶段需要添加什么约束呢?

本篇博文提供了一个示例,用于演示如何使用 Python 脚本调试赛灵思 PCIe 设计。此处提供的技巧可应用于所有设计,而非仅供 PCIe 专用。

请问下截图所示的是不是指内核所需要使用的硬件资源比例? 遇到下面的报错时,该如何排查和避免问题呢?

本文介绍MATLAB的混频测试

该视频展示了即将推出的业界首款 Versal HBM 设备的稳健性,并展示了 HBM 堆栈在芯片上的高带宽利用率。

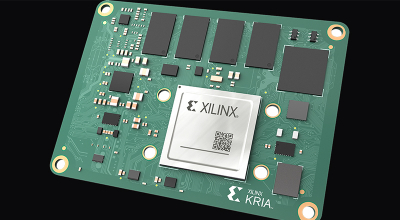

本文将介绍 Xilinx 提供的灵活系统级模块 (SOM) 解决方案,开发人员能用它来快速实现边缘部署的智能摄像头解决方案。