Versal ACAP CIPS 和 NoC (DDR) IP 核配置

judy 在 周三, 04/20/2022 - 16:14 提交

本文描述了如何在设计的早期阶段使用 Xilinx® Power Estimator (XPE) 工具进行功率分析。

赛事以培养学生从算法到硬件加速的能力为主,除了万元奖励外,参赛同学将获得与学术界、产业界广泛交流的机会。

Xilinx的技术生态做的非常好,基本上所有常用的IP核都有官方例程供开发者学习,咱不用白不用,今儿咱就一起白嫖他一手----从官方例程开始学习如何具体使用这个IP核。

阅读本文将有助于你的FPGA选型和设计过程,并且有助于你规避许多难题。

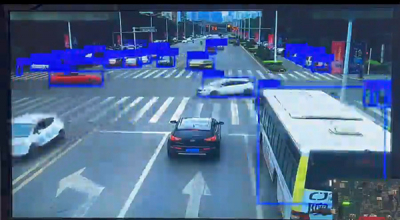

Avnet Smart Model Select 应用是一个示例设计,它演示了如何将 Vitis 视频分析 SDK 示例设计 作为 Kria 加速应用部署至 KV260 视觉 AI 入门套件。

IP是什么?简单来讲,IP就是Xilinx或者第三方开发者把自己的逻辑模块封装成一个黑盒子,然后拿出来给别人用。那什么又是黑盒子?

Vitis 嵌入式平台创建所需要注意的问题

当运行一个基于DPU的应用程序时,当平台中的DPU和编译后的XMODEL之间存在架构不匹配时,就会发生指纹错误。

本文介绍Vivado IP Integrator中实现DFX(Dynamic Function eXchange)的快速入门