AI 计算加速如何继续提升效率

judy 在 周三, 05/18/2022 - 10:03 提交

本直播将为您详细介绍在 AI Benchmark 的测试中能达到90%以上的计算效率的 AI 芯片,以及如何使用 VCK5000 加速 AI计算的设计方法和设计资源。

本直播将为您详细介绍在 AI Benchmark 的测试中能达到90%以上的计算效率的 AI 芯片,以及如何使用 VCK5000 加速 AI计算的设计方法和设计资源。

采用任意精度数据类型,可以在获得相同精度的运算条件下,运算速度更快且使用更少的资源。

本文我们介绍FPGA外设DDR2/DDR3硬件设计相关内容,包括PCB板层数估计,信号端接、信号完整性及时序考虑等问题。

本文描述在 Versal® ACAP 中实现电源排序的各种方法。

该视频介绍了电源域和电源状态的概念,以及如何在您的设计中使用 Ultra96 实现电源域切换。

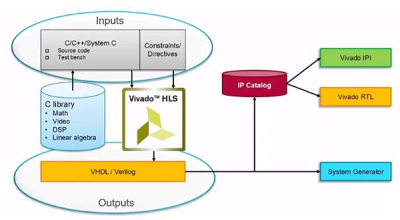

本文我们通过一个具体的实例,演示HLS设计流程。

Vitis 统一软件平台 2022.1现已推出!

Vivado® ML 2022.1 在 Vivado ML 标准安装中可支持 Versal Premium VP1202、VP1502、VP1702 和 VP1802 器件。

搭载赛灵思 Zynq RFSoC 架构的 Evenstar RU 使用相同的基础硬件即可提供能够满足广泛应用需求的灵活性,包括4G/5G、毫米波和 sub-6GHz。

传统的FPGA RTL设计流程主要是采用VHDL、VerilogHDL或System Verilog进行工程的开发,同时也是通过硬件描述语言来编写测试案例对开发的工程进行仿真验证