vitis 2021.1 zynq flash固化bug解决方法

judy 在 周二, 05/31/2022 - 15:45 提交

在使用vitis 2021.1 版本的过程中发现,在使用flash固化时会出现错误,导致固化失败。具体情况如下

在使用vitis 2021.1 版本的过程中发现,在使用flash固化时会出现错误,导致固化失败。具体情况如下

随着越来越多的设备正在智能化,例如具备互联网连接功能、通常还有摄像头的嵌入式处理器,数据创建正以指数级的速度呈爆炸式增长。人工智能和高性能计算正在改变计算领域

通过本视频,您将了解 AMD-Xilinx 的自适应计算技术如何助力开发 ABB Robotics 的最新系列协作机器人 GoFa™。

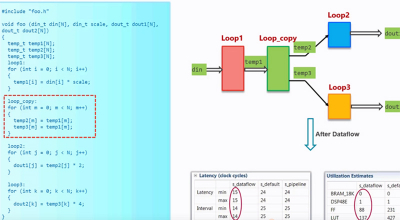

本文通过例子中来解释for循环中的基本概念

本次将分上下篇介绍基于Xilinx Zynq UltraScale+ RFSoC ZCU216评估套件的详细内容

本视频介绍了可编程逻辑 (PL) 电源管理。PL 时钟控制是最有效的电源管理方法。

Zynq UltraScale+ RFSoC 是业界首款单芯片自适应无线电平台,在一款芯片内集成射频直采数据转换器、单芯片软决策前向纠错核(SD-FEC)、FPGA逻辑、完整的ARM处理器子系统和高速收发器等。

6月28日,10:00 – 11:30。AMD 工业与视觉系统架构师,翁羽翔将座客直播间与您详细介绍我们最新发布的 KR260 机器人入门开发套件。

6月9日,上午10:00 – 11:30, AMD Xilinx 携手iWaySense 举行线上直播《看 FPGA 如何赋能传统汽车后视镜》与大家共同探讨这个即将开启的千亿级规模的汽车前装市场。

本文以JTAG to AXI Master调试AXI BRAM 控制器举例说明 JTAG 到 AXI Master 的使用方法。