Vitis HLS命令

joycha 在 周四, 03/31/2022 - 10:49 提交

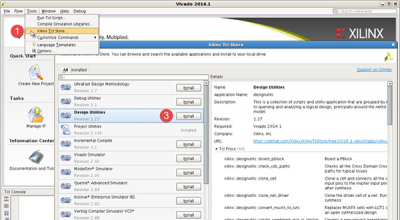

vitis_hls 命令默认以 GUI 模式打开。要查看哪些选项可用于vitis_hls,可以使用-help选项

vitis_hls 命令默认以 GUI 模式打开。要查看哪些选项可用于vitis_hls,可以使用-help选项

在IC领域中常用的脚本有Tcl、Perl、Shell、Python等,在这些脚本里面,Tcl(“工具命令语言”)由于其语法简单,易上手等特点,在FPGA开发中越来越受到重视。

本快捷参考指南重点介绍了关键的设计方法步骤,有助于更快达成系统集成与设计实现,从而利用赛灵思器件与工具最大限度创造价值,同时也提供了相关辅助资料的链接。

当试图在Vitis HLS工具中编写高效的C++时,你需要谨慎使用模数运算符。这是因为C = A % B等同于C = A - B * (A / B)。换句话说,模运算符在功能上等同于三种操作

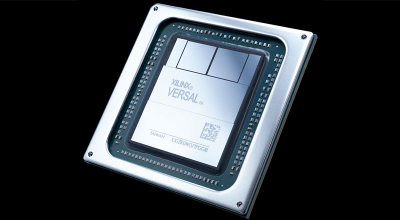

从数据中心到边缘部署,我们的 7nm Versal® 自适应计算加速平台( ACAP ) 产品组合持续在多个行业迎来重要里程碑。今天,我们很高兴宣布,Versal HBM 系列现正面向早期试用客户出货。

2022年4月8日10:00-12:00,AMD-赛灵思高级产品市场经理王宏强先生将带来主题演讲:如何用赛灵思VCK5000 AI引擎实现全线加速

我们一直推荐用户在FPGA板卡硬件调试中使用IBERT测试transceiver,以便于排除电源、参考时钟和连接介质的问题,确保transceiver可以正常进行用户需要的高速串行设计调试。

在KV260 AI入门开发套件简介中提到KV260有四个参考例程,smartcam是其中之一,下面介绍一下如何使用Petalinux编译smartcam应用,以及如何编译smartcam,使用vivado打开工程。

在PetaLinux 2020.1时分享了在PetaLinux里为模块创建补丁。现在使用PetaLinux 2021.2, 发现类似命令会报告错误。

实际使用中,Tandem PROM最为简单,Tandem PCIe由于允许通过PCIe进行重配置,因此在服务器领域最为常用。本文只介绍Tandem PROM方式。