如何在 HLS 设计中推断 UltraRAM?

judy 在 周二, 03/15/2022 - 11:22 提交

为了推断UltraRAM,你需要在所需的内部阵列上使用一个资源指令。

为了推断UltraRAM,你需要在所需的内部阵列上使用一个资源指令。

该演示展示了 Xilinx DPD 性能,分别来自 Ampleon 和 Wolfspeed 的高功率驱动器和末级 PA。该演示展示了 Zynq RFSoC DFE 以及 Xilinx 最新 DPD IP 如何线性化用于 C 波段的高功率宏系列。

每个新处理器都声称是最快,最便宜或最省电的,但是如何衡量这些声明和支持信息呢?

了解 Zynq Ultrascale+ MPSoC 的快速数据处理如何帮助 Elinvision 捕获人脚的准确测量值。

WWG(有线/无线通信部)执行副总裁兼总经理 Liam Madden 将与大家探讨如何灵活利用自适应计算提供的解决方案来适应 5G 基础设施的演进。

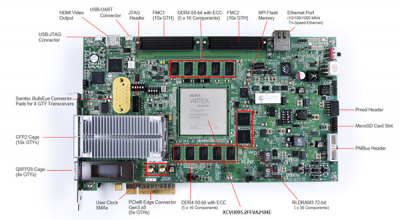

本文将为大家介绍FPGA原型验证的魅力,以及贸泽电子在售的极具市场竞争力的FPGA产品和相关的开发套件。

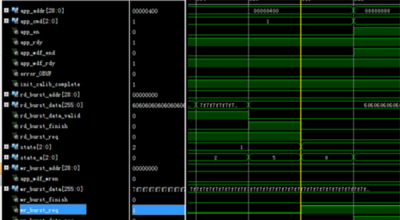

DDR接口信号分为DDR对外接口信号、用户应用接口信号和读写控制信号。对外接口信号直接与DDR芯片连接,用户应用接口信号为DDR控制器IP输出信号

本文描述了针对Versal® ACAP的PID控制器设计与模型合成器。

Vitis视觉库是一个FPGA加速视觉功能的集合,类似于OpenCV中的功能。虽然这些内核的实现并不依赖于OpenCV,但许多视觉库的功能都提供了示例设计测试平台,使用OpenCV来演示加速内核的功能。

最近几天读了Xilinx网站上一个很有意思的白皮书,名字叫《Get Smart About Reset:Think Local, Not Global》,在此分享一下心得,包括以前设计中很少注意到的一些细节