简要讲解Xilinx SRIO IP(高速收发器二十八)

judy 在 周一, 02/17/2025 - 09:50 提交

SRIO是串行RapidIO的简写,其实现代比较常用的高速接口协议,比如SRIO、PCIE、JESD204B等都是基于SERDES开发的,均属于高速串行总线

SRIO是串行RapidIO的简写,其实现代比较常用的高速接口协议,比如SRIO、PCIE、JESD204B等都是基于SERDES开发的,均属于高速串行总线

在最新的DisplayPort 1.4 RX Subsystem IP GUI界面, 有使能Video EDID的选项, 如下:

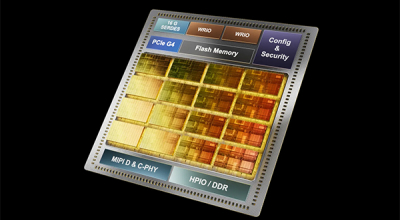

莱迪思Nexus 2凭借其领先的低功耗、高性能和小尺寸在可持续产品类别中获得认可。

继发布 AMD Virtex UltraScale+ FPGA PCIE3.0 开发平台 AXVU13P 后,ALINX 进一步研究尖端应用市场,面向 AI+ 场景进行优化设计,推出 AXVU13F。

为使大规模 MIMO 系统的商业化成为现实,AMD推出了采用RF 级模拟技术的全可编程(All Programmable)RFSoC,该方案在集成方面取得了突破性的进展

近期在后台收到好几位朋友咨询一些关于HyperRAM的问题,熊猫君在这里简单的做一个总结。

RFSoC平台作为最先进的现代SDR平台,可以使用FPGA可编程逻辑内核生成GHz带宽信号,上变频、滤波、数字预失真甚至射频载波调制都可以通过数字方式进行

IP是什么?简单来讲,IP就是Xilinx或者第三方开发者把自己的逻辑模块封装成一个黑盒子,然后拿出来给别人用。那什么又是黑盒子?

下一代仪器设备(如示波器、分析仪、信号源和生成器)支持跨不同类型端点的主机至器件、器件至主机以及对等通信

Virtex UltraScale+XCVU13P提供了大规模的可编程逻辑资源、丰富的DSP和存储资源,以及高速串行接口,可满足各种高端应用的严苛性能需求。