斯巴鲁基于 AI 的 EyeSight 安全系统集成 AMD 自适应计算技术

judy 在 周三, 02/12/2025 - 09:35 提交

EyeSight 系统采用两个摄像头,其设计类似于人眼,可以从三维角度检测车辆前方的其他车辆、物体及行人,并准确判断每个物体的距离、形状和速度

EyeSight 系统采用两个摄像头,其设计类似于人眼,可以从三维角度检测车辆前方的其他车辆、物体及行人,并准确判断每个物体的距离、形状和速度

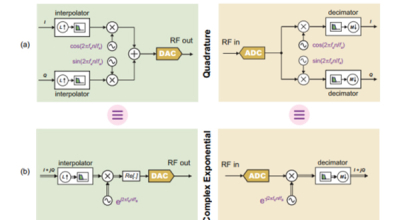

RFSoC的RFDC块可以配置为对复输入输出和实输入输出进行处理。RF-ADC可以单独用于实输入,也可以成对用于正交或复输入

为高频交易公司开发硬件一直是 FPGA 工程师最热门的职位之一。由于该行业提供的高薪,甚至可以被称为该领域许多人的“梦想职业”

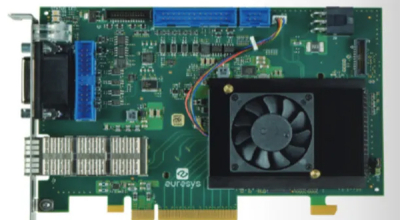

CoaXPress标准是一种先进的非对称串行高速视觉标准。在机器视觉应用中,主要采用CoaXPress标准作为相机和图像采集卡之间高速图像数据传输的数字接口

与单载波调制相反,使用QAM的动机是带宽效率。调幅信号所需要的带宽为基带带宽的两倍,可以说AM的效率只有50%,QAM允许提高效率

Aurora协议在Xilinx的FPGA上有两种实现方式:8B/10B 与 64B/10B。两个协议大部分相同,主要区别在编码方式上

了解VPX和VNX+如何在恶劣环境中提供高可靠性和高性能,并保护模块免受冲击、振动和极端温度的影响。

该项目开源了一个基于FPGA的机械键盘,它可以并行地为每个按键实现输入和去抖动功能,使用STM32F723 MCU以8Khz的频率与主机进行480Mb/s的USB高速通信

本文将UART用作硬件通信协议应遵循的标准步骤进行说明,讨论使用UART的基本原则,重点是数据包传输、标准帧协议和定制帧协议

AMD公布2024年第四季度及年度财报。2024年第四季度营业额达到创纪录的77亿美元,毛利率为51%,经营收入8.71亿美元,净收入4.82亿美元