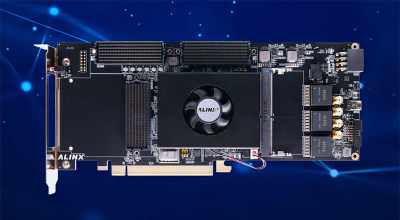

ALINX 发布 AXVU13P:AMD Virtex UltraScale+ FPGA PCle 3.0 开发平台

judy 在 周一, 12/23/2024 - 14:46 提交

这款搭载 AMD 16nm 工艺 XCVU13P 芯片的高性能开发验证平台,凭借卓越的计算能力和灵活的扩展性,专为应对复杂应用场景和高带宽需求而设计

这款搭载 AMD 16nm 工艺 XCVU13P 芯片的高性能开发验证平台,凭借卓越的计算能力和灵活的扩展性,专为应对复杂应用场景和高带宽需求而设计

今天刷了一下国产Fpga的网站,发现高云新出的Arora V系列的GW5AT系列的FPGA在接口扩展和桥接领域的应用很有特色

Enclustra开发的手持式频谱分析仪具有实时信号处理路径。它包括精心设计的滤波、下变频、傅立叶变换以及对所得信号重要特性的分析

MIPI D-PHY IP包含TX(Master)及RX(Slave)两个子系统模块,可根据应用需求单独配置

全新第五代 AMD EPYC(霄龙)处理器——AMD EPYC 9005 系列处理器专为加速数据中心、云计算和 AI 工作负载而设计,助力企业将计算性能提升到全新水平。

Virtex Ultrascale+ XCVU13P提供了大规模的可编程逻辑资源、丰富的DSP和存储资源,以及高速串行接口,可满足各种高端应用的严苛性能需求。

本文以Mircon公司的SDRAM芯片MT48LC64M4A2的数据手册为例,学习一下SDRAM的自动刷新操作,并进行仿真验证其正确性。

Example design simulation是同一个器件的GTM仿真。如果需要做两个芯片GTM对接的仿真,可以用两个GTM wizard,生成example

为了在物理无线信道上发送数字数据,在载波调制之前,必须首先使用基带调制方案将其从位转换为符号。这个过程被称为基带调制

从最初学FPGA到现在,遇到过太多bug,但都没有写过博客记录,因为多数问题都比较简单且网上有比较好的答案