Versal ACAP, RPU - 为调试寄存器 DBGDSAR 设置的值错误

judy 在 周一, 06/07/2021 - 14:21 提交

每个 RPU 处理器都有 1 个 DBGDSAR 寄存器,其中包含其 CoreSight ROM 表的偏移地址。但是,读取 RPU 的 DBGDSAR 寄存器会返回以下不正确的偏移值:

每个 RPU 处理器都有 1 个 DBGDSAR 寄存器,其中包含其 CoreSight ROM 表的偏移地址。但是,读取 RPU 的 DBGDSAR 寄存器会返回以下不正确的偏移值:

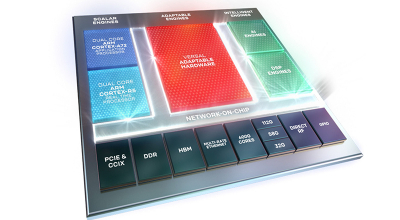

当赛灵思首次出现在以汽车为主题的Auto Tech 2021展会时,它显示出两个强烈的信号:1、自动驾驶的市场热度开始进入一个新的拐点;2、为数不多的拥有先进典型处理架构的芯片巨头正在加快在汽车领域跑马圈地的节奏。

本视频介绍如何使用赛灵思FPGA为数据库工作负载和分析负载提速。

Vivado可以导出脚本,保存创建工程的相关命令和配置,并可以在需要的时候使用脚本重建Vivado工程。脚本通常只有KB级别大小,远远小于工程打包文件的大小,因此便于备份和版本管理。下面把前述脚本升级到Vivado 2020.2为例,讨论如何升级Vivado工程脚本。

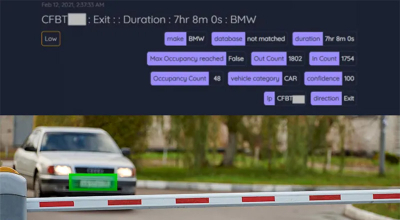

自从 4 月份公开发布 Kria SOM 产品组合以来,赛灵思应用商店中涌现出大量新的边缘应用。作为发布、推广和销售来自赛灵思生态系统合作伙伴的优秀应用的一站式平台,赛灵思应用商店现在为边缘端和云端提供了多种加速应用和 IP 解决方案。

本视频围绕赛灵思Alveo U250通用FPGA加速器构建的一款真正激动人心的新产品。这是首款通用FPGA加速虚拟机,其将被作为微软Azure的一部分发布,FPGA工作负载的云迁移,让开发人员充分利用云端的强大功能采取的简化措施。

在任何一致的 ACE 系统中,启用 WriteUnique/WriteLineUnique (WU/WLU) 传输事务后,如果在有一项或多项高速缓存逐出事务处于暂挂状态时尝试执行存储,那么写回无分配 (WBNA) 存储可能发生停滞。

在 Github 上探索 60 多个综合性 Vitis 教程,涵盖硬件加速器、运行时和系统优化、机器学习等

2021年,赛灵思为广大开发者朋友准备了丰富的年度活动,其中 KRIA™ SOM系列沙龙已经拉开帷幕,只等你来!

我们常说“大道至简”,因为往往用词越多,想法就越具体、越琐碎,所以当我们在开发 Kria™ SOM (System-on-Module,系统模块) 时,就大胆提出了“无需 FPGA 设计也可尽享赛灵思技术优势”这一概念。