Cadence 推出 Palladium Z3 和 Protium X3 系统,开启加速验证、软件开发和数字孪生新时代

judy 在 周三, 12/25/2024 - 11:09 提交

与前一代产品相比,Cadence 新一代“动力双剑”组合的容量增加超过 2 倍,速度快 1.5 倍,可助力设计人员快速开发先进芯片,满足生成式 AI、移动、汽车、超大规模和 LLM 应用的需求

与前一代产品相比,Cadence 新一代“动力双剑”组合的容量增加超过 2 倍,速度快 1.5 倍,可助力设计人员快速开发先进芯片,满足生成式 AI、移动、汽车、超大规模和 LLM 应用的需求

第二代 AMD Versal AI Edge 系列自适应 SoC 的异构架构允许使用单芯片解决方案处理自动驾驶系统的所有阶段 —— 检测、感知、规划和执行

在全球半导体产业蓬勃发展的浪潮中,FPGA(现场可编程门阵列)以其高度的灵活性和可编程性,成为众多创新应用的基石。

本文将详细介绍PolarFire®片上系统(SoC)Discovery工具包的技术细节及其优点。

采用先进的Agilex™ 5 FPGA的SoM可以满足边缘应用日益增长的需求,这些应用要求以更低功耗实现更高性能

设计一个4Lanes SLVS-EC桥接到2组4lanes MIPI DPHY接口的电路模块

本文简要讲解一下I2S协议,该协议包含ADCRC(ADC采集数据的左右声道指示信号)

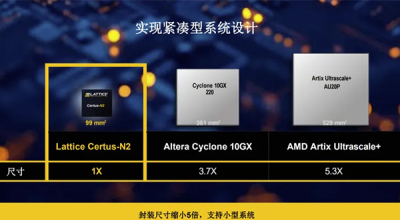

本文介绍了莱迪思Nexus 2平台在推出时与其他现有的同类FPGA的比较分析。分析包括功耗、启动时间、尺寸和安全特性

这款搭载 AMD 16nm 工艺 XCVU13P 芯片的高性能开发验证平台,凭借卓越的计算能力和灵活的扩展性,专为应对复杂应用场景和高带宽需求而设计

今天刷了一下国产Fpga的网站,发现高云新出的Arora V系列的GW5AT系列的FPGA在接口扩展和桥接领域的应用很有特色