AMD Alveo 媒体加速产品组合 SDK 1.2.1 发布

judy 在 周三, 12/18/2024 - 17:23 提交

我们很高兴地宣布 AMD Alveo 媒体加速产品组合( AMA )SDK 1.2.1 版本发布,从而进一步扩展 AMD Alveo MA35D 媒体加速卡功能

我们很高兴地宣布 AMD Alveo 媒体加速产品组合( AMA )SDK 1.2.1 版本发布,从而进一步扩展 AMD Alveo MA35D 媒体加速卡功能

由于Sensor采集到的颜色分量曲线与人眼对颜色分量的感知曲线不一致,所以会导致拍摄的图像呈现在人眼前时感觉与真实世界相去甚远

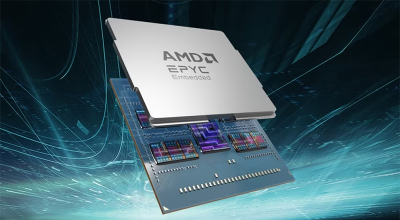

第四代 AMD EPYC 嵌入式处理器为网络、安全、存储及工业系统提供突破性能和能效

Versal器件上DDR4硬核控制器DDRMC跑仿真时,按照IP的默认设置,在IP wizard中使能了“Internal Responder”

营收排名全球第三的FPGA企业莱迪思(Lattice Semiconductor)正在面临增长难题。当前,全球半导体产业在经历全行业下行周期后普遍回暖,“逆势而行”的莱迪思将如何破局?

FPGA并没有像软件那样用已有的cache,FPGA的HLS编译器会在FPGA中创建一个快速的memory architecture以最好的适应算法中的数据样式(data layout)

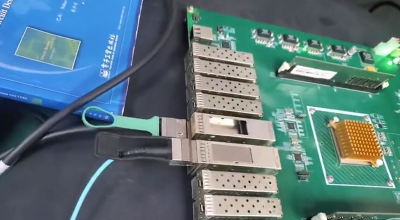

本文简单的介绍一种通过FPGA来对基于四通道serdes的40G/10G以太网接口PMA和PCS层进行链路连接测试的方法

在高性能计算(HPC)领域,SmartNIC获得了巨大的吸引力。为了实现最高性能,HPC环境需要高处理能力、高效的数据移动和高速互连

在快速发展的技术领域,从以云端为中心到以网络边缘为中心的创新转变正在重塑数据的处理和利用方式。

京微齐力展示了最新研发并已实现量产的22nm产品——HME-P3系列FPGA芯片