ADI为何收购了Flex Logic?

judy 在 周五, 11/29/2024 - 16:17 提交

这是这个月(2024年11月)最让我惊讶的消息。Analog Devices (ADI) 收购了 Flex Logic。

这是这个月(2024年11月)最让我惊讶的消息。Analog Devices (ADI) 收购了 Flex Logic。

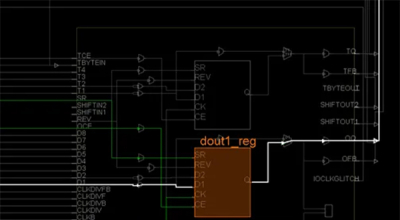

本文主要是讲解ODDR的工作模式,并对工作模式进行仿真,同时将OLOGIC的使用方式进行讲解

接收机从本质上说是发射机的反向实现,但在设计上更为复杂。接收机首先把输入的射频信号下变频为中频信号,然后进行解调

环回(loopback)是GT的一种特殊配置模式。可以把发送端的数据直通过自身PMA层或对方器件(不加进一步处理)后再转回给发送器件的接收端

本文对Xilinx 7 Series Intergrated Block for PCI Express PCIe硬核IP进行简要介绍

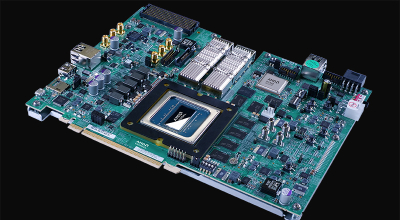

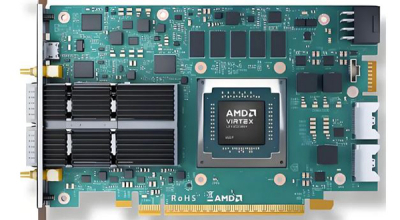

随着开放式无线接入网络(ORAN)架构的采用,电信行业正在经历一场重大变革。这种创新的网络设计方法带来了解聚合和互操作性

据彭博社报道,总部位于美国俄勒冈州希尔斯伯勒的莱迪思(Lattice)正在考虑对英特尔旗下的FPGA业务Altera发起收购要约。这一消息在FPGA市场引起了轩然大波

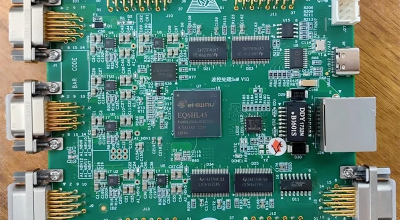

本文介绍的波控处理软硬一体解决方案主要是面向相控阵天线控制领域,波控处理通过控制不同天线组件的幅相来调整天线波束的方向和增益

本白皮书概述了使用 VNP4 进行设计的优点。

这样在频率a载波下产生了双边带信号:a+b和a-b,而对于信号传输来说,其实只需要一个信号即可。