FPGA串口实战篇

judy 在 周四, 08/29/2019 - 10:15 提交

在业界,串口又称为通用异步收发器(Universal Asynchronous Receiver/Transmitter,简称UART),它的通信方式遵循一套串口协议:UART通信首先将接收到的并行数据换成串行数据来传输。数据帧从起始位开始,后面是7个或8个数据位,一个可用的奇偶校验位和一个或几个高位停止位

在业界,串口又称为通用异步收发器(Universal Asynchronous Receiver/Transmitter,简称UART),它的通信方式遵循一套串口协议:UART通信首先将接收到的并行数据换成串行数据来传输。数据帧从起始位开始,后面是7个或8个数据位,一个可用的奇偶校验位和一个或几个高位停止位

赛灵思技术日活动(Xilinx Technology Day,XTD)旨在通过一系列精炼的、跨越多个市场应用的深度技术分享活动,助力广大开发者迅速把握赛灵思全球领先的平台及技术的最新消息和应用案例,从而加速您将创新理念变为现实的进程。9月17日,XTD 活动成都站即将拉开帷幕,在此我们诚邀您参加这场面向创新领域,聚焦行业热点的技术盛会。

根据市场调研公司的报告显示,到2021年,直播视频将达到700亿美元规模,而非直播视频内容将达到接近1000亿美元规模,且直播视频流量增速大于非直播视频,2023年有可能超越非直播视频。视频处理成就了近两千亿的市场商机,也成为未来服务器的最大负载之一

本文是关于Hot Chips 31大会观察与思考的系列文章的第二部分。整个系列将介绍我在Hot Chips大会上的几点观察与思考,涵盖以下几点内容:

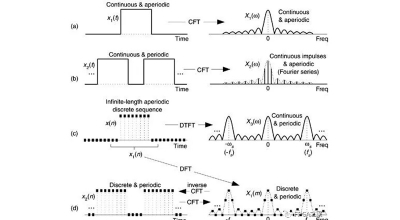

本文只涉及各种傅利叶之间的概念关系,不考虑数学严谨性。

要在设计中精确建模外部时序,必须为输入和输出端口提供时序信息。Xilinx Vivado集成设计环境(IDE)仅在FPGA边界内识别时序,因此必须使用以下命令指定超出这些边界的延迟值

本文主要介绍I2C总线相关的一些基本概念、通信流程、同步和仲裁、模式切换等。

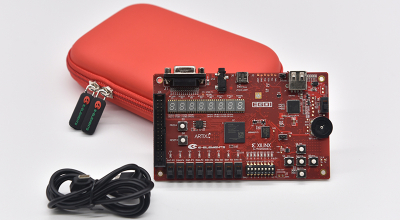

软件:Vivado2017.4 板卡:Ego1 型号:xc7a35tcsg324-1

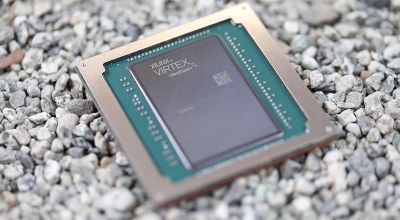

本文详细介绍了 Alveo™ U280 数据中心加速卡,它是采用了 Xilinx® Virtex® UltraScale+™ 技术的标准 PCIe® (Peripheral Component Interconnect express) Gen3 x16 加速卡。

Xilinx 推出全球容量最大的 FPGA - Virtex® UltraScale+™ VU19P,不仅能实现当今最先进 ASIC 和 SoC 技术的原型与模拟设计,还能支持各种复杂的新兴算法。