用最小的 RISC-V 核心挑战 FPGA 极限

judy 在 周三, 05/21/2025 - 09:39 提交

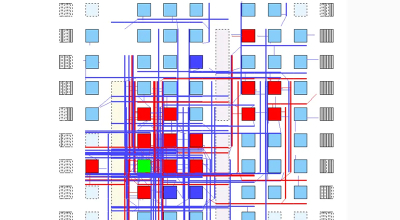

CoreScore 是一个开源项目,旨在通过部署尽可能多的 SERV 核心(世界上最小的 RISC-V 处理器)在 FPGA 上,评估 FPGA 的资源承载能力和综合布线工具的效率。

CoreScore 是一个开源项目,旨在通过部署尽可能多的 SERV 核心(世界上最小的 RISC-V 处理器)在 FPGA 上,评估 FPGA 的资源承载能力和综合布线工具的效率。

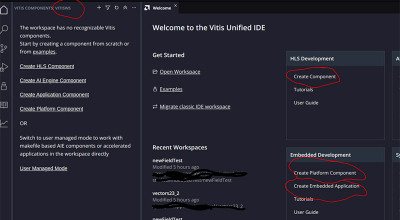

这篇博客是在上一篇博客 Vitis HLS 系列 1 的基础上撰写的,但使用的是 Vitis Unified IDE,而不是之前传统版本的 Vitis HLS。

5月,一年一度的紫光同创Workshop系列活动正式启航,硬核产品发布、干货技术分享及精彩应用案例展示,燃动湾区,为深圳和广州两地开发者带来了一场FPGA技术交流盛宴!

本文将为那些设计 FPGA 电源电路的人介绍在 FPGA 电源设计中需要了解的要求,以及 ADI μ Module® (微型模块) 稳压器作为符合这些要求的电源模块。

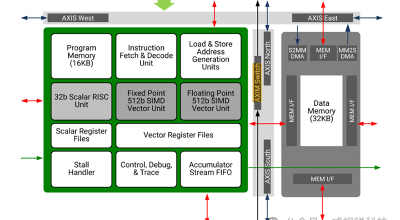

AI引擎是一系列超长指令字处理器,具有单指令多数据向量单元,针对计算密集型应用进行了高度优化,特别是数字信号处理、5G无线应用和机器学习等AI技术。

随着工业领域向实现工业4.0的目标不断迈进,市场对具备弹性连接、低功耗、高性能和强大安全性的系统需求与日俱增。

本篇博文旨在将 O-RAN 仿真系列博客扩展至多个分量载波 (CC) 的用例。其中还涉及到 O-RAN 通道处理 (OCP) 模块中的 CCID 配置。

在FPGA领域,商业工具长期垄断架构设计与验证的「解释权」。而来自多伦多大学的VTR-Verilog-to-Routing项目,以开源代码掀开了FPGA的「黑盒子」

在上篇文章中,我们已经通过测试图案生成器,成功验证了 ALINX VD100 的图像显示链路。这次终于要接入 MIPI 摄像头,进行真正的图像处理了!

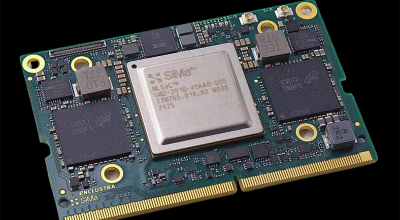

Lynx SAI50采用50 TOPS机器学习加速器 (MLA),在69.6mmx45mm的紧凑外形中提供高性能AI处理能力