自行科技梁波:基于Zynq的ADAS解决方案!

judy 在 周四, 12/20/2018 - 10:13 提交

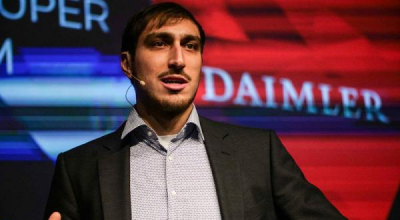

12月18日,AVNET嵌入式视觉中国区研讨会在上海洲际酒店隆重举办。Xilinx、Avnet、Onsemi、Infineon、Maxim等国内外知名品牌齐聚一堂,共同探讨与交流嵌入式视觉设计的灵感与经验。作为AVNET在国内的重要合作伙伴,自行科技受邀参加此次盛会,公司项目总监梁波做了“Autocruis 基于Zynq的ADAS解决方案”的主题演讲,受到现场嘉宾与观众的热烈反响

12月18日,AVNET嵌入式视觉中国区研讨会在上海洲际酒店隆重举办。Xilinx、Avnet、Onsemi、Infineon、Maxim等国内外知名品牌齐聚一堂,共同探讨与交流嵌入式视觉设计的灵感与经验。作为AVNET在国内的重要合作伙伴,自行科技受邀参加此次盛会,公司项目总监梁波做了“Autocruis 基于Zynq的ADAS解决方案”的主题演讲,受到现场嘉宾与观众的热烈反响

人工智能的出现,摩尔定律的放缓,这些趋势正在影响全球范围内的每个人。作为行业的领导者, 赛灵思积极地拥抱这些趋势, 而且通过不断地突破自我,将赛灵思塑造成指数级变化的技术、商业模式和市场的推动者。为应对这种市场趋势,赛灵思推出了ACAP 平台。

本篇主要介绍PCIe总线相关的信号

用HDL语言+Vivado创建一个挂载在AXI总线上的自定义IP核

本篇主要针对Zynq UltraScale + MPSoC的DDR接口,从硬件设计的角度进行详细介绍,最后展示一下小编之前自己设计的基于ZU+的外挂8颗DDR4的设计

本视频重点介绍了 Vivado 设计套件 2018.3 版本中的新增功能,包括对操作系统以及器件的支持情况,还有高层次增强功能,以及各种功能改进以加速设计集成、实现和验证的过程

首先,需要的肯定是Ubuntu操作系统。可以在自己的电脑上安装物理机,也可以是虚拟机下运行的。我的是在Vmware下运行的Ubuntu14.04 32位操作系统。由于zedboard上的Linux操作系统跑的是32位的,为了省去麻烦,我没有安装64位的

戴姆勒智能车饰技术经理Thomas Kaelberer应邀出席赛灵思CTO Ivo Bolsens的主题演讲,首度公布了两家公司合作研发的人工智能车载系统的详细信息。

在上周刚刚举行的赛灵思开发者大会( 法兰克福站)上,戴姆勒智能车饰技术经理Thomas Kaelberer应邀出席赛灵思CTO Ivo Bolsens的主题演讲,首度公布了两家公司合作研发的人工智能车载系统的详细信息。

本教程旨在指导用户通过 Plunify Cloud 的云服务器,来使用 InTime 软件优化 FPGA 设计