MachXO5D-NX:加密敏捷和硬件可信根“双剑合璧”,让网络威胁无处遁形

judy 在 周二, 07/09/2024 - 14:52 提交

MachXO5D-NX-15D/55TD两款产品分别拥有14K/53K逻辑单元密度和16/146个18 X 18乘法器。与MachXO5T-NX FPGA一样,MachXO5D-NX-55TD同样支持PCIe Gen 2硬核模块

MachXO5D-NX-15D/55TD两款产品分别拥有14K/53K逻辑单元密度和16/146个18 X 18乘法器。与MachXO5T-NX FPGA一样,MachXO5D-NX-55TD同样支持PCIe Gen 2硬核模块

在赛灵思器件中为部分重配置编译设计时,会创建不同类型的比特流。本文档为 7 系列和 UltraScale 器件的每种比特流类型定义了术语,并进行了详细说明。

本文介绍写SD卡的理论知识,主要包括SD卡分类、容量、速度、管脚、物理结构以及命令控制等。

本文将详细介绍Verilog中的编译指令,帮助大家更高效地进行硬件设计。

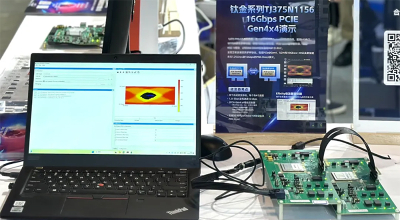

正常情况下, PCIe EP和Host同时启动,Host给EP提供参考时钟,双方协商后建立PCIe链路。

RapidIO 互连架构旨在与最流行的集成通信处理器、主机处理器和网络数字信号处理器兼容,是一种高性能、分组交换互连技术

I/O Die产品ML100结合了UCIe IP和HBM IP,包含16个标准封装的UCIe接口与1个完整的HBM 控制器,其带宽约为1TB/s,与HBM3完美匹配

ABI Research的数据显示,预计到2024年底,设备端AI推理功能将覆盖60%的设备。但许多可以利用人工智能和机器学习(AI/ML)功能的网络边缘设备

TJ375支持16对16Gbps SerDes接口以及两组PCIE Gen4x4协议接口,为高带宽通信提供充足支撑

在Lattice看来,采用从硬件到软件的多层安全方法,利用现场可编程门阵列(FPGA)技术,对于计算、通信和工业市场的公司来说,有效保护系统免受复杂攻击并符合新要求至关重要。