P4 Suite for FPGA面市,优势何在?

judy 在 周四, 07/25/2024 - 14:44 提交

P4 Suite for FPGA是一款综合性工具套件,可在数字网络的不同领域提供广泛功能,该套件能够以高达200 Gbps甚至更高的数据传输速率支持FPGA

P4 Suite for FPGA是一款综合性工具套件,可在数字网络的不同领域提供广泛功能,该套件能够以高达200 Gbps甚至更高的数据传输速率支持FPGA

很多初学者刚开始看到PCIe IP文档时,不太懂Xilinx PCIe IP核主要的数据接口:CC、CQ、RQ、RC。本文主要就是对这些接口做详细的介绍,希望能答疑解惑。

今天我们分享几个用FPGA实现的小型神经网络,侧重应用。

活动内容包括主题演讲和分组会议、技术培训,以及来自生态系统合作伙伴和行业领导者的各类FPGA技术演示

思尔芯凭借与AMD的长期紧密合作受邀参与此次盛会。思尔芯副总裁陈英仁先生并发表精彩技术演讲。深刻剖析了在当前RISC-V、Chiplet、人工智能及汽车电子等领域蓬勃发展的背景下

AMD今日宣布,AMD 总裁 Victor Peng 将于 2024 年 8 月 30 日退休。他将继续担任 AMD 执行团队的顾问,并支持过渡,直至退休。

日前发布的《中国智算服务市场(2023下半年)跟踪》报告显示,2023年下半年,中国智算服务市场整体规模达到114.1亿元人民币,同比增长85.8%。

本文将深入探讨Verilog中的可综合设计与不可综合设计,揭示它们之间的差异,并提供一些建议参考。

本文档旨在描述推荐的设计方法,帮助您在设计输入期间有效利用 AMD 的 Versal™ 自适应 SoC 资源。

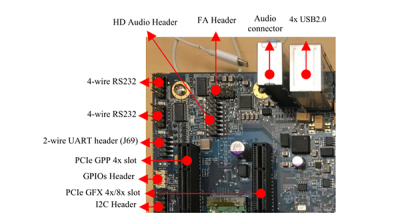

Ubuntu 20启动时,自动加载了UART驱动,系统启动信息含有UART的相关信息。