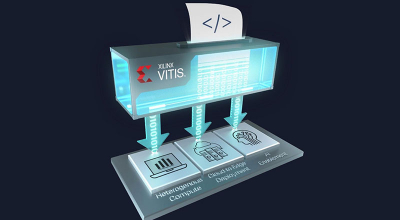

Vitis/Vitis AI 直播课第二堂:Vitis 设计流程(含Alveo加速卡Vitis实例操作)

judy 在 周三, 03/18/2020 - 10:00 提交

软件工程师如何借助赛灵思统一软件平台Vitis将算法提速数倍?

如何快速打造从云到端可自适应的经得起时间检验的应用?

如何快速上手Vitis?

软件工程师如何借助赛灵思统一软件平台Vitis将算法提速数倍?

如何快速打造从云到端可自适应的经得起时间检验的应用?

如何快速上手Vitis?

本案例利用PYNQ自定义Overlay驱动Respeaker,实现了一个智能音箱。ReSpeaker是一个四路ADC芯片AC108位转换芯片的四通道麦克风的设备,它支持I2S接口,在本案例中它需要连接到PYNQ-Z2的树莓派接口。

叮叮当铃儿响叮当

万众瞩目的 Versal Premium 正式亮相

先来看大家是如何评价它的 ↓

本项目介绍了超声波测距模块的使用,展示了如何将超声波测距模块测到的距离定量地表示在LED灯条上,会学习到PYNQ框架中对Microblaze软核编程的方法以及其它的PYNQ基本API使用。

调查数据显示,2019 年区域流量容量提升了100 倍,带宽年复合增长率达到了 51%。面对流量洪峰、面对数据大爆炸,算力不足问题开始凸显并得到越来越多企业的重视。在这样的时代背景下,以出色算力提升企业运作效率的 FPGA 博得了诸多互联网公司的青睐

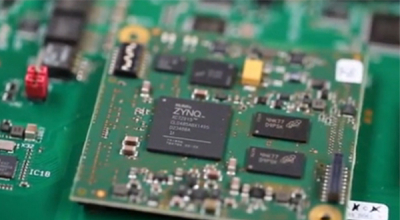

如今随着技术的进步,各类嵌入式应用对于架构本身的设计灵活性与功耗性能比提出了更加严苛的要求。瑞萨电子推出了基于Xilinx Zynq-7000的电源时钟管理方案,通过集成了Xilinx基于28nm Artix®-7或Kintex®-7的可编程逻辑,从而实现了出色的功耗性能比与最大的设计灵活性

FPGA 在系统中逐渐由配角变成主角,从普通的胶合逻辑扩展到业务处理,从应用于原型验证扩展到大规模应用于量产设备中。今天的可编程平台已经是最多拥有数百万六输入查找表的强大处理器件

有图 有数 有 真相

HDL Verifier 能够让开发 FPGA 和 ASIC 设计的设计验证工程师直接从 Simulink 模型生成 UVM 组件和测试平台,并在支持 UVM 的仿真器(比如来自 Synopsys、Cadence 和 Mentor 的仿真器)中使用这些组件和测试平台

今天上午,FPGA发领头羊赛灵思公司以在线发布形式宣布推出 Versal ACAP 产品组合第三大产品系列—— Versal™ Premium,这款FPGA堪称是史上最强大FPGA,它有高度集成且功耗优化的网络硬核,是业界带宽最高、计算密度最高的自适应平台