Versal ACAP RPU - 为调试寄存器 DBGDRAR 设置的值错误

judy 在 周四, 05/13/2021 - 09:39 提交

每个 RPU 处理器都有 1 个 DBGDRAR 寄存器,其中包含 CoreSight 根 ROM 表的地址。但读取此寄存器时会返回错误的地址 0xfe800003。正确的返回地址应为 0xf0800003。尝试访问包含错误地址的 CoreSight 根 ROM 表将导致 RPU 处理器发生软件异常。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

每个 RPU 处理器都有 1 个 DBGDRAR 寄存器,其中包含 CoreSight 根 ROM 表的地址。但读取此寄存器时会返回错误的地址 0xfe800003。正确的返回地址应为 0xf0800003。尝试访问包含错误地址的 CoreSight 根 ROM 表将导致 RPU 处理器发生软件异常。

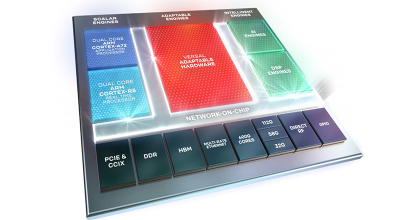

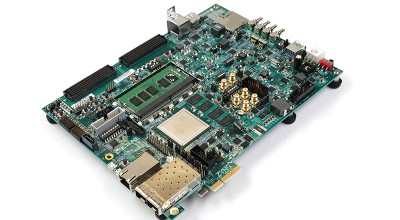

不久以前,从算法到现场机器学习( ML )模型仍然需要经历漫长而复杂的道路。对于一些企业而言,如果能够接触到具有神经网络部署经验的 ML 专家,则可能会有一些选择,但其开发工作却非常耗时。赛灵思依托 Vitis 统一软件平台以及近期推出的 KRIA SOM (System-on-Module),缩短了这一过程。

MPSoC的MAC支持1588。在Linux Kernel的配置项中使能CONFIG_MACB_USE_HWSTAMP,并在Linux rootfs添加Linux ptp/ethtool,就可以运行1588的软件命令ptp4l。

如果用户设计在可编程逻辑中明确强制使用数据 IMUX 寄存器,那么逻辑函数可能不正确。IMUX 寄存器旨在用于进行 Vivado 自动时序最优化。Vivado 设计工具会在时序最优化期间对 IMUX 寄存器进行相应管理,以避免发生此错误。

在测试MPSoC VCU的编解码时,经常需要使用NV12 YUV文件。YUV文件很大,所以经常依靠解压MP4等文件来产生NV12 YUV文件。 FFMpeg是一个强大的工具,可以用来从MP4文件生成NV12 YUV文件。

在 FPGA 设计进程中,时序收敛无疑是一项艰巨的任务。低估这项任务的复杂性常常导致工作规划面临无休止的压力。赛灵思提供了诸多工具,用于帮助缩短时序收敛所需时间,从而加速产品上市。本篇博文描述了一种方法,能够有效减少时序路径问题分析所需工作量

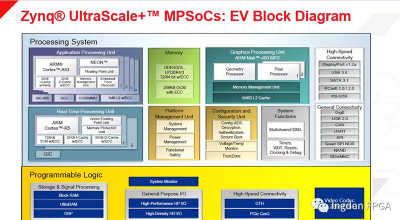

部分 ZynqUltraScale+MPSoC的可编程逻辑(PL)中包含最新的视频编码器/解码器。这种新型硬化编解码器能够访问来自PL 或PS的视频和音频流,以提供和/或存取达到软件算法50倍的压缩视频信息,从而节省宝贵的系统存储空间

MPSoC含有PS、PL;在PS和PL之间有大量接口和信号线,比如AXI、时钟、GPIO等。缺省情况下,PS和PL之间有接口和信号线被关闭。加载bit后,软件才会打开PS和PL之间的接口和信号线。比如在文件xfsbl_partition_load.c中,FSBL加载FPGA的bit后会执行下列操作,打开PS和PL之间的接口和信号线

处理器可使用等待事件 (wait for event, WFE) 或等待中断 (wait for interrupt, WFI) 机制来进入低功耗状态。仅当嵌入式跟踪宏单元 (Embedded Trace Macrocell, ETM) 耗尽 AMBA ATB 接口上的所有跟踪字节后,处理器才能进入低功耗状态。

MPSoC是带ARM处理器和FPGA(PL)的SoC,包含4核A53及其常用外部模块(PS)。A53(PS)使用Arm GIC-400,属于GICv2架构。如果想了解GIC-400的具体细节,请参考文档APU GIC: CoreLink GIC-400 Generic Interrupt Controller, DDI 0471B, r0p1。