一文看懂FPGA原型验证的技术进阶之路

judy 在 周二, 03/16/2021 - 15:18 提交

目前ASIC的设计变得越来越大,越来越复杂,单片FPGA已不能满足原型验证要求,多片FPGA验证应运而生。RTL逻辑的分割、多片FPGA之间的互联拓扑结构、I/O分配、高速接口都对应用FPGA原型验证的芯片开发者提出了更高的要求也带来了前所未有的挑战。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

目前ASIC的设计变得越来越大,越来越复杂,单片FPGA已不能满足原型验证要求,多片FPGA验证应运而生。RTL逻辑的分割、多片FPGA之间的互联拓扑结构、I/O分配、高速接口都对应用FPGA原型验证的芯片开发者提出了更高的要求也带来了前所未有的挑战。

本文针对上海证券交易所的行情发布系统,采用Verilog硬件描述语言,在FPGA加速卡上开发了对行情信息流的以太网,IP和UDP以及FAST协议的硬件解码,设计了支持指令集编程的微指令加速引擎。与传统的基于软件的方法相比,本文提出的专用硬件处理方案延时可降低10倍以上。

有很多客户在比较 FFT C-Model 仿真和 FFTIP 前仿遇到问题。今天赛灵思技术专家对此提出三种原因和解决办法。

示波器的需求急速成长,同时新的研究和测试应用也需要更多、更快、更复杂的讯号。 这会需要更具智能功能的测试设备,才能准确侦测特定的讯号状况并避免空滞时间、在采集期间处理资料以缩短测试时间,或者是快速产生反馈讯号以控制待测装置 (DUT)。 过去十年来,强大 PC 软件和模块化 I/O 的紧密整合,不仅缩短了测试时间,同时也降低了整体测试成本

P4改变了网络格局,因为它允许表达自定义数据包处理。近年来,有几篇著作将P4程序映射到FPGA。但是,这些工作大部分都集中在实现数据包解析器或match action阶段。迄今为止,尚未有报道提出关于FPGA的通用数据包逆解析的原理。推荐一篇2021年FPGA顶会会议论文,介绍基于FPGA开源200Gbps数据包逆解析器的设计与实现。

由 Ubuntu 16.04 机器上不兼容 GTK 版本导致的 Eclipse GUI 问题

在本系列的前几篇文章中 ,我们讨论了 Dennard Scaling 和摩尔定律的细目以及对专用和适应性加速器的需求。 然后,我们深入研究了功耗问题,并讨论了网络压缩的高级优势。在这第三篇文章中,我们将探讨专门构建的“计算有效”神经网络模型的优点和挑战。

在软件开发过程中我们经常遇到用 patch 来传递和更新代码的场景。今天赛灵思技术专家以一个端到端的例子来演示在 Petalinux 使用过程中,如何给 u-boot 的源码生成patch 并在 Petalinux 中进行编译。

Petalinux可以帮助工程师简化内核模块的创建工作。在petalinux工程目录下,使用命令“petalinux-create -t modules --name --enable”,能创建Linux内核模块,包括c源代码文件、Makefile、Yocto的bb文件。相关文件放在目录“project-spec/meta-user/recipes-modules”,目录结构如下

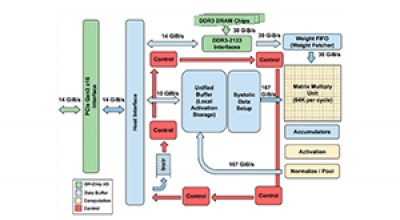

在 "人工智能引发能源问题,我们该怎么办 (一)"中,我们简要介绍了更高层次的问题,这些问题为优化加速器的需求奠定了基础。作为一个尖锐的问题提醒,现在让我们通过一个非常简单的图像分类算法,来看一看与之相关联的计算成本与功耗。