白皮书 | 赛灵思 AI 引擎及其应用

judy 在 周三, 09/30/2020 - 10:40 提交

针对 5G 蜂窝和机器学习 DNN/CNN 等计算密集型应用,赛灵思的新型矢量处理器 AI 引擎由 VLIW SIMD 高性能处理器阵列构成,与传统的可编程逻辑解决方案相比,功耗减半,芯片计算密度提升高达 8 倍。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

针对 5G 蜂窝和机器学习 DNN/CNN 等计算密集型应用,赛灵思的新型矢量处理器 AI 引擎由 VLIW SIMD 高性能处理器阵列构成,与传统的可编程逻辑解决方案相比,功耗减半,芯片计算密度提升高达 8 倍。

数据已经成为数字经济时代最重要的生产要素,成为企业和机构的核心资产,而数据价值的体现则是数据的隐私保护。传统的面向静态数据保护的安全手段已经无法满足数据在跨企业、跨机构之间流通的需求

Xilinx VCU TRD 集成了图像和视频编解码功能,生成的根文件系统比较大,2020.1的rootfs.cpio.gz大约有114MB。工程师可以根据自己需要裁剪,减少根文件系统大小。

在Ubuntu下,解压rootfs.cpio.gz,得到rootfs.cpio,再解压,得到就是文件了。

赛灵思为 FPGA 和 MPSoC 器件中所有受支持的 I/O 标准提供了 I/O 缓存信息规范 (I/O Buffer Information Specification, IBIS) 模型。本篇博文旨在提供有关如何为可编程逻辑 (PL) 和处理器系统 (PS) 多用途 I/O (MIO) 进行 IBIS 模型名称解码的指导信息。

本设计使用Ultra96开发板,使用InceptionV3网络,以及Vitis-AI的量化编译工具链,制作了一个五花分类装置。利用Xilinx的DPU(Deep learning Processing Unit)IP,Vitis-AI工具链,快速的在FPGA上部署深度学习网络。

有工程师反映,在编译PetaLinux工程时,出现大量Taskhash mismatch错误。工程还没有编译完成,检查build.log,已经出现超过200个的Taskhash mismatch错误

Vitis统一软件平台可以在包括FPGA、SoC和Versal ACAP在内的异构Xilinx平台上开发嵌入式软件和加速应用程序。它为加速边缘计算、云计算和混合计算应用程序提供了统一的编程模型。

有工程师反映,根据MPSoC SWDT在Standalone下的例子xwdtps_polled_example.c,不能实现MPSoC的PS复位。

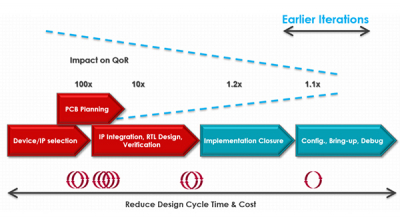

FPGA 设计是有章可循的,如果用的是 Xilinx 的 FPGA,这个“章”就是 UG949。最新版的 UG949 是 2020.1 版本,整个文档共六大章节 306 页(点击此处查看《UltraFast 设计方法指南》)。对于如此之多的内容该如何消化吸收呢?首先,了解一下 UG949 的背景信息。

智能手机似乎迎来了“智能”化的时代,并掀起了物联网(IoT)革命。那么,是什么让 SmartNIC 实现了智能化?是硬件、编程还是其他什么?