FPGA设计干净的代码是程序员的核心技能

judy 在 周二, 08/20/2019 - 10:06 提交

一个项目看上去很简单,精心设置了架构,结果越做发现冲突越多,直到整个逻辑完全混乱。本来一天可以的完成的事不知道怎么搞的一个星期还没有完成;本来只需要做一行更改,结果却涉及到N个模块;出现了一个非常小的BUG打了一个补丁

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

一个项目看上去很简单,精心设置了架构,结果越做发现冲突越多,直到整个逻辑完全混乱。本来一天可以的完成的事不知道怎么搞的一个星期还没有完成;本来只需要做一行更改,结果却涉及到N个模块;出现了一个非常小的BUG打了一个补丁

本文介绍两种LVDS数传接口:GMSL和FPD Link,这两种接口在汽车视频传输方面的应用是比较广泛的,尤其是Camera和处理器之间的链路,通过STP或者同轴电缆能使整个链路达到15m。

1、FPD Link

卷积占据了CNN网络中绝大部分运算,进行乘法运算通常都是使用FPGA中的DSP,这样算力就受到了器件中DSP资源的限制。比如在zynq7000器件中,DSP资源就较少,神经网络的性能就无法得到提升。利用xilinx器件中LUT的结构特征,设计出的乘法器不但能灵活适应数据位宽,而且能最大限度降低LUT资源使用

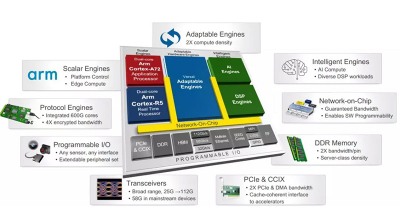

ACAP是Xilinx推出的一种革命性异构计算架构,计划在今年10月份推出。它将标量计算,可编程逻辑还有矢量计算结合在一起,充分利用各自的优势,不仅仅增强了针对各种机器学习算法的适用性,也提高了计算密度和存储带宽。其中AI engine和NoC是新颖的设计,FPGA和CPU的结合早在zynq系列中已经应用

以交换机设计为例。在交换机设计前期,转发表项是固化在交换机内部的(给FPGA片内BRAM初始值),但是在测试过程中,往往需要对表项进行修改,如果直接修改BRAM的coe文件,则需要重新综合、实现、生成bit文件,其中,综合与实现耗时十分严重,设计规模越大,消耗的时间越长,而生成bit文件消耗的时间则相对固定

本文主要介绍基于zynq的IIC的驱动架构,通过代码编写来深入了解IIC驱动的内容和机制。

本文转载自CSDN李锐博恩Reborn某校招题目,仅仅给出下面电路图,要求画出Q1,Q2以及Q3的波形,并描述电路功能。可以看出,这个电路很简单,或许你会纠结于初值是什么,可是仔细想想,该电路其实和初值没有关系

Xilinx新一代 SOC,Zynq UltraScale+ MPSOC系列性能强悍无比,相比ZYNQ 7000系列每瓦性能提升5倍,作为一 名电子发烧友,都想体验一把这高性能的MPSOC开发板。现在用米尔MPSOC开发板来一个hello world。

下载modelsim,这里用的是modelsim10.4版本。完成下载和安装,在安装文件夹中可以看到uvm-1.1d,这是我们使用的uvm版本。在uvm-1.1d/win64下有uvm_dpi.dll文件,这是已经编译过的uvm库。

在实际开发中,我们会经常使用到LCD屏,LCD屏的种类有很多种,对应的使用方法也有所不同,但是,在ZYNQ 图像传输开发中,思路大体类似,下面介绍在ZYNQ中,使用LCD显示OV5640图像方法