ZYNQ常用外设设计 (下)

demi 在 周一, 09/02/2019 - 12:03 提交

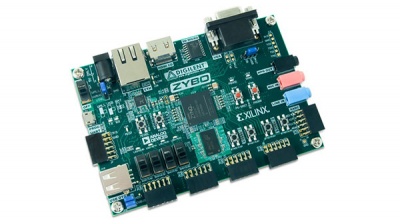

ZYNQ有专用的DDR Controller接口,如果外部硬件连接了DDR器件,于是在ZYNQ Processing System中正确配置了相应的信号和参数后,DDR就可以成为ZYNQ的内存,在SDK中可以直接使用memcpy、memset以及类似的函数对于Memory空间进行操作。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

ZYNQ有专用的DDR Controller接口,如果外部硬件连接了DDR器件,于是在ZYNQ Processing System中正确配置了相应的信号和参数后,DDR就可以成为ZYNQ的内存,在SDK中可以直接使用memcpy、memset以及类似的函数对于Memory空间进行操作。

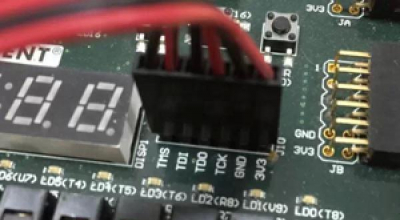

本文主要介绍JTAG总线的引脚定义、接口标准、边界扫描和TAP控制器。JTAG(Joint Test Action Group;联合测试行动小组)是一种国际标准测试协议(IEEE 1149.1兼容),主要用于芯片内部测试。

ZYNQ学习过程中一个重要环节是进行调试,当然在SDK中进行调试时,设置断点进行单步调试非常高效。但是ZYNQ中毕竟涉及到FPGA的硬件部分,于是如果可以通过UART与ZYNQ器件进行双向的通信会使得调试非常方便。

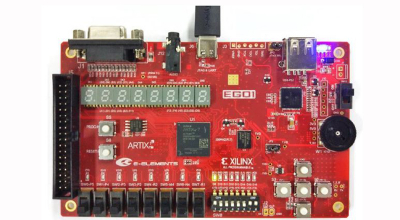

随着人们安防意识的不断增强和智能技术的持续发展,针对用户对安全系数高的智能电子锁的需求,使用FPGA蓝牙通信技术设计了基于FPGA蓝牙通信技术的智能电子锁系统。通过手机APP直接控制电子锁,对电子锁进行双重加密处理,具有开锁、修改密码,管理员控制用户开锁信息表,增添和删除能开锁的用户信息等功能。经测试,系统使用方便,动态灵活,安全可靠

本文主要介绍I2C总线的读写操作流程。I2C总线的操作包括读和写,具体的操作流程如下:

时钟网络反映了时钟从时钟引脚进入FPGA后在FPGA内部的传播路径。报告时钟网络命令可以从以下位置运行:

Zynq UltraScale+ MPSoC的PS有以下主要特点:一个四核64位ARM Cortex-A53处理器,带L1和L2级缓存和ECC功能,可单独上电和关电;Cache一致性互联单元为PS和PL提供双向Cache一致性保证;SMMU(系统内存管理)单元用于PS和PL虚拟内存管理;双核ARM Cortex-R5F处理器(带浮点扩展),可运行在锁步模式或独立工作模式

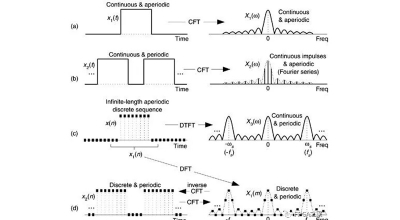

本文只涉及各种傅利叶之间的概念关系,不考虑数学严谨性。

要在设计中精确建模外部时序,必须为输入和输出端口提供时序信息。Xilinx Vivado集成设计环境(IDE)仅在FPGA边界内识别时序,因此必须使用以下命令指定超出这些边界的延迟值

本文主要介绍I2C总线相关的一些基本概念、通信流程、同步和仲裁、模式切换等。