Xilinx中解决高扇出的方法

demi 在 周日, 09/29/2019 - 16:37 提交

Fanout,即扇出,指模块直接调用的下级模块的个数,如果这个数值过大的话,在FPGA直接表现为net delay较大,不利于时序收敛。因此,在写代码时应尽量避免高扇出的情况。但是,在某些特殊情况下,受到整体结构设计的需要或者无法修改代码的限制,则需要通过其它优化手段解决高扇出带来的问题。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

Fanout,即扇出,指模块直接调用的下级模块的个数,如果这个数值过大的话,在FPGA直接表现为net delay较大,不利于时序收敛。因此,在写代码时应尽量避免高扇出的情况。但是,在某些特殊情况下,受到整体结构设计的需要或者无法修改代码的限制,则需要通过其它优化手段解决高扇出带来的问题。

静态时序分析是检查IC系统时序是否满足要求的主要手段。以往时序的验证依赖于仿真,采用仿真的方法,覆盖率跟所施加的激励有关,有些时序违例会被忽略。此外,仿真方法效率非常的低,会大大延长产品的开发周期。静态时序分析工具很好地解决了这两个问题。

在fpga工程中加入时序约束的目的: 1、给quartusii 提出时序要求; 2、quartusii 在布局布线时会尽量优先去满足给出的时序要求; 3、STA静态时序分析工具根据你提出的约束去判断时序是否满足的标准。

在Xilinx ISE中不同的操作都有不同的文件类型对应,例如综合、布局、布线、生成比特流等都会产生特定格式的文件,在vivado中也是一样,只不过在vivado中,文件的格式相比于ISE中更加同一。

Python 中字符串是由 Uniocde 编码的字符组成的不可变序列,它具备与其它序列共有的一些操作,例如判断元素是否存在、拼接序列、切片操作、求长度、求最值、求元素的索引位置及出现次数等等。除此之外,它还有很多特有的操作,值得我们时常温故学习,所以,今天我就跟大家继续聊聊字符串。

一个程序块可以有多个initial和always过程块。每个initial和always说明语句在仿真的一开始同时立即开始执行;initial语句只执行一次,而always语句则不断重复的活动着,直到仿真结束。

IBUFDS、IBUFGDS和OBUFDS都是差分信号缓冲器,用于不同电平接口之间的缓冲和转换。

M-PCIe即Mobile PCIe,主要应用对象是智能手机等嵌入式设备。PCI-SIG在PCIe Spec V3.1中引入基于MIPI M-PHY V2.0的M-PCIe。相比于标准的PCIe总线,M-PCIe ECN主要的改动在物理层,通过引入M-PHY,旨在获得更低的功耗以适应嵌入式设备的低功耗要求。

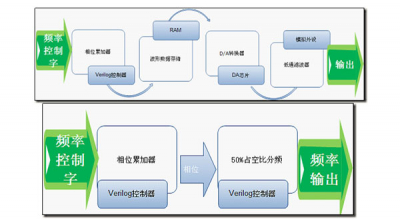

在大部分的教科书中,都会提到如何分频,包括奇数分频,偶数分频,小数分频等。首先讲述DSS(直接频率合成法)的原理。DDS是重要的频率合成方法,在波形发生器中有极其重要的应用。DDS主要由几部分组成:a) 相位累加器;b) RAM数据读取;c) D/A转换器;d) 低通滤波器。

根据维基百科定义:字符串是由零个或多个字符组成的有限序列。而在Python 3中,它有着更明确的意思:字符串是由Unicode码点组成的不可变序列(Strings are immutable sequences of Unicode code points.)