Vitis AI:从边缘到云的最佳人工智能推断

demi 在 周五, 10/11/2019 - 10:27 提交

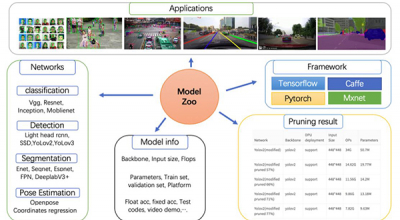

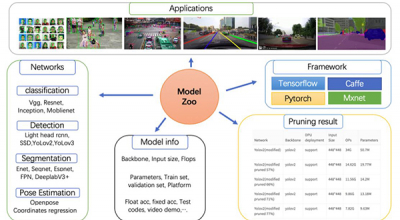

Vitis™ AI 是 Xilinx 的开发平台,适用于在 Xilinx 硬件平台(包括边缘设备和 Alveo 卡)上进行人工智能推断。它由优化的 IP、工具、库、模型和示例设计组成。Vitis AI 以高效易用为设计理念,可在 Xilinx FPGA 和 ACAP 上充分发挥人工智能加速的潜力。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

Vitis™ AI 是 Xilinx 的开发平台,适用于在 Xilinx 硬件平台(包括边缘设备和 Alveo 卡)上进行人工智能推断。它由优化的 IP、工具、库、模型和示例设计组成。Vitis AI 以高效易用为设计理念,可在 Xilinx FPGA 和 ACAP 上充分发挥人工智能加速的潜力。

在“设置”对话框的“约束”部分下,选择“默认约束设置”作为活动约束设置;包含在Xilinx设计约束(XDC)文件中捕获的设计约束的一组文件,可以将其应用于设计中。

Vitis 统一软件平台包括:全面的内核开发套件,可无缝构建加速的应用;完整的硬件加速开源库,针对 Xilinx 硬件平台进行了优化;插入特定领域的开发环境,可直接在熟悉的更高层次框架中进行开发;不断发展的硬件加速合作伙伴库和预建应用生态系统。

首先来理清楚MIO与EMIO的关系。MIO是PS的I/O引脚,一共有54个,分为Bank0与Bank1,可以接许多外设比如UART、SPI或GPIO等,另外可以引脚复用。

FPGA是可编程芯片,因此FPGA的设计方法包括硬件设计和软件设计两部分。硬件包括FPGA芯片电路、 存储器、输入输出接口电路以及其他设备,软件即是相应的HDL程序以及最新才流行的嵌入式C程序。

如果将计算机比作人的话,CPU就是人的大脑,而PCIe就是人的神经中枢,负责内部数据信息的传输。

PCI,英文全称:PeripheralComponent Interconnect,外围组件互联,由Intel于1991年提出。随着Intel Pentium处理器诞生而迅速发展,当时几乎所有的外围设备,从硬盘控制器、声卡、显卡和网卡,都使用PCI插槽来连接到计算机的主板上。

-flatten_hierarchy——full: 综合时将原始设计打平,只保留顶层层次,执行边界优化;none: 综合时完全保留原始设计层次,不执行边界优化;rebuilt: 综合时将原始设计打平,执行边界优化,综合后将网表文件按照原始层次显示,故与原始层次相似。

Verilog中提供了四种循环语句,可用于控制语句的执行次数,分别为:for,while,repeat,forever。其中,for,while,repeat是可综合的,但循环的次数需要在编译之前就确定,动态改变循环次数的语句是不可综合的。forever语句是不可综合的,主要用于产生各种仿真激励。

本文标题的问题分为两部分:(1)Python 中是否支持复制字符串?(2)如果不支持,为什么不支持?请读者花几分钟想一下,想清楚后,把你的答案记住,然后再往下看。