MIPI系列之“M-PHY”

judy 在 周四, 01/24/2019 - 09:19 提交

本篇主要介绍MIPI物理层规范中的M-PHY,主要包括M-TX和M-RX状态机、M-PHY的配置流程、M-PHY的电气特性等。MIPI M-PHY专为需要快速通信通道以实现高分辨率图像,高视频帧速率和大型显示器或存储器的数据密集型应用而设计。它是一种多功能PHY,为工程师提供配置选择和跨行业平台开发的能力,以有效地解决多个市场

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

本篇主要介绍MIPI物理层规范中的M-PHY,主要包括M-TX和M-RX状态机、M-PHY的配置流程、M-PHY的电气特性等。MIPI M-PHY专为需要快速通信通道以实现高分辨率图像,高视频帧速率和大型显示器或存储器的数据密集型应用而设计。它是一种多功能PHY,为工程师提供配置选择和跨行业平台开发的能力,以有效地解决多个市场

本文列出了能够与 Vivado 设计套件联用的支持性第三方仿真器。

本文主要介绍以太网Drive Side接口(MAC和PHY之间的接口),也被称为MII(Media Independent Interface),支持从10M到100G的不同应用场合,主要包括MII、RMII、SMII(Cisco Systems Specification)、SSMII、S3MII、GMII、RGMII、SGMII、QSGMII(Cisco Systems Specification)、TBI、RTBI、XGMII、XAUI、RXAUI、XLGMII、XLAUI、CGMII、CAUI、HIGIG(Broadcom Specification)、Interlaken等接口

现今,使用FPGA技术进行射频数据信号处理已经非常普遍,因为该技术可实现高速计算能力。通常情况下,处理大量RF数据需要部署的FGPA资源越来越多。因此,FPGA模块会跨多个处理子系统进行部署。借助FlexRIO FPGA模块和LVDS数字接口模块,ST Kinetics成功地设计并实现了一个解决方案

在介绍ODDR之前,我们先简单了解一下OLOGIC。OLOGIC块在FPGA内的位置紧挨着IOB,其作用是FPGA通过IOB发送数据到器件外部的专用同步块。OLOGIC 资源的类型有OLOGIC2(位于HP I/O banks)和OLOGIC3(位于HR I/O banks)。

本文主要介绍以太网Line Side对外接口,也被称为MDI(Media Dependent Interface),包括电口和光口。其中光模块主要针对10G以下的,10G以上的本文就不做介绍了。

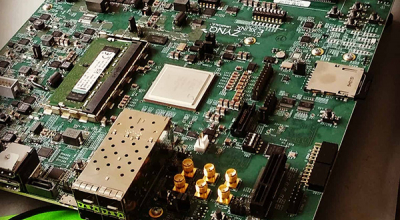

本文主要介绍Xilinx FPGA的配置模式,主要包括Master/Slave模式,Serial/SelectMAP模式,JTAG模式等。其中7系列只有Logic部分,其配置相关功能引脚全部连接到FPGA端的特定bank上;Zynq 7000系列既有PL部分,也有PS部分,其JTAG从PL侧引出,其余配置相关引脚全部从PS侧引出

Python 是一门用途广泛、易读、而且容易入门的编程语言。但同时 python 语法也允许我们做一些很奇怪的事情。

神经网络(NN)几乎可以在每个领域帮助我们用创造性的方式解决问题。本文将介绍神经网络的相关知识。读后你将对神经网络有个大概了解,它是如何工作的?如何创建神经网络?

本篇主要介绍Xilinx FPGA的电源设计,主要包括电源种类、电压要求、功耗需求,上下电时序要求,常见的电源实现方案等。