使用Vivado生成.MCS文件

judy 在 周五, 03/08/2019 - 10:42 提交

其实生成.mcs文件非常简单,但是只是对有经验的设计者而言。对于新手,生成一个.MCS文件可能就会遇到各种各样的问题。下面就简单的介绍一下如何生成.MCS文件。

这里介绍两种种方法。第一种是使用GUI,也就是用鼠标点来点去就可以。另外一种就是用tcl命令

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

其实生成.mcs文件非常简单,但是只是对有经验的设计者而言。对于新手,生成一个.MCS文件可能就会遇到各种各样的问题。下面就简单的介绍一下如何生成.MCS文件。

这里介绍两种种方法。第一种是使用GUI,也就是用鼠标点来点去就可以。另外一种就是用tcl命令

下面我挑选出的这几个技巧常常会被人们忽略,但它们在日常编程中能真正的给我们带来不少帮助。

随着高速数据传输的普及,Serdes已经成为FPGA上重要的I/O接口。而线速率也不断的提高。更高的线速率也就带来了更大的通道衰减影响。通常,Serdes接收端需要打开内部的均衡来对高速串行信号进行处理

随着需求的多样化,FPGA的功能也进一步的增强。其中,高速收发器从本来是只有高端FPGA才有的模块,已经变为相对普及的甚至必备的功能模块。而10G的线速率也从多年前的少数FPGA支持,变为目前的主流线速率

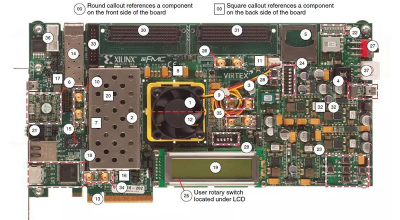

FPGA开源工作室将通过五篇文章来给大家讲解xilinx FPGA 使用mig IP对DDR3的读写控制,旨在让大家更快的学习和应用DDR3。本实验和工程基于Digilent的Arty Artix-35T FPGA开发板完成。

FPGA开源工作室将通过五篇文章来给大家讲解xilinx FPGA 使用mig IP对DDR3的读写控制,旨在让大家更快的学习和应用DDR3。本实验和工程基于Digilent的Arty Artix-35T FPGA开发板完成。

本来写了一篇关于高速收发器的初步调试方案的介绍,给出一些遇到问题时初步的调试建议。但是发现其中涉及到很多概念。逐一解释会导致文章过于冗长。所以单独写一篇基本概念的介绍,基于Xilinx 7系列的GTX

对于mig与DDR3/DDR2 SDRAM的读写时序我们不需要了解太多,交给mig就可以了。我们需要做的是控制好User Interface,写出正确的User logic。想要写好Userlogic,我们就必须清楚每一个用户控制接口的含义

随着FPGA在数据中心加速和Smart NIC在SDN和NFV领域的广泛应用,基于以太网接口的FPGA开发板越来越受到关注。而更高速率的以太网接口技术则是应用的关键,本文将详细介绍基于FPGA的10G以太网接口的原理及调试技术。

FPGA开源工作室将通过五篇文章来给大家讲解xilinx FPGA 使用mig IP对DDR3的读写控制,旨在让大家更快的学习和应用DDR3。本实验和工程基于Digilent的Arty Artix-35T FPGA开发板完成。软件使用Vivado 2018.1