【视频教程】:Model Composer 2018.3 新功能

judy 在 周四, 04/18/2019 - 15:04 提交

观看本视频,了解赛灵思 Model Composer 2018.3 版本中的重要更新。Model Composer 是一个利用 Vivado 高层次综合技术的 MathWorks Simulink 附加工具。视频将介绍包括控制设计吞吐量、在仿真过程中调试导入的 C/C++ 函数、以及如何使用自带的入门示例等内容。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

观看本视频,了解赛灵思 Model Composer 2018.3 版本中的重要更新。Model Composer 是一个利用 Vivado 高层次综合技术的 MathWorks Simulink 附加工具。视频将介绍包括控制设计吞吐量、在仿真过程中调试导入的 C/C++ 函数、以及如何使用自带的入门示例等内容。

Xilinx Zynq SoC提供了一个新的系统设计能力。本课程给经验丰富的系统架构师提供了如何在一颗芯片中架构一个Zynq SoC系统。主要介绍ARM® Cortex™-A9 processor-based处理系统和集成的可编程逻辑资源,可供系统设计师成功而有效的利用

Vivado® Design Suite 提供两种方法可加速产品上市进程,提高工作效率。可构建 Vivado 布局布线。在任何设计阶段处理任何类型的 ECO 问题,并可加快运行时间,确保时序收敛进程。

作者:张浩 ,来源:FPGA技术联盟

10. case,casez,casex语句

Verilog定义了case,casez和casex语句,用于做多种情况下的选择语句。

reg [1:0] sel;

reg [2:0] result;

首先告诉大家,我们所说的“路径”的是后者——trajectory。我们看一下这两种“路径”在机械臂的世界里有什么区别。

在接触Verilog 语法参考手册的时候,我们发现其提供了一组非常丰富的功能来描述硬件。所以大家往往会疑惑那些Verilog语句是可综合的,那些是只能用于写Testbench的,其实,参考手册中只有一小部分语句是可综合的,但是这一小部分可综合的语法确是我们应用最为频繁的

Python简单易学,但又博大精深。许多人号称精通Python,却不会写Pythonic的代码,对很多常用包的使用也并不熟悉。学海无涯,我们先来了解一些Python中最基本的内容。

【干货分享】Get到这些小技巧,FPGA设计将提高一个台阶

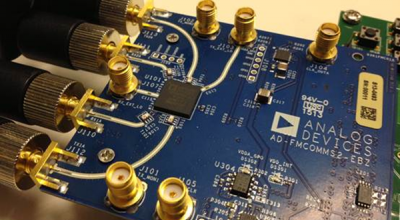

JESD204B是一种新型的基于高速SERDES的ADC/DAC数据传输接口。随着ADC/DAC采样速率的不断提高,数据的吞吐量也越来越大,对于500MSPS以上的ADC/DAC,动辄就是几十个G的数据吞吐率,而采用传统的CMOS和LVDS已经很难满足设计要求,这个时候,JESD204B应运而生。现在各大厂商的高速ADC/DAC上基本都采用了这种接口

今天发布一个Vivado 下固化 FLASH的压缩和提高加载速度的技巧和方法。这个方法对于需要快速加载程序的场合特别有用比如PCIE 需要满足200MS的加载时间才能实现上电后系统能够识别到开发板。