详解FPGA的串口通讯(UART)

judy 在 周三, 05/22/2019 - 14:17 提交

UART作为异步串口通信协议的一种,工作原理是将传输数据的每个字符一位接一位地传输。其中每一位(Bit)的意义如下:

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

UART作为异步串口通信协议的一种,工作原理是将传输数据的每个字符一位接一位地传输。其中每一位(Bit)的意义如下:

电路的核心逻辑是组合电路,比如异步的FIFO/RAM读写信号、地址译码信号等电路;电路的输出不依赖于某一个时钟,也就说不是由时钟信号驱动触发器产生的;异步电路非常容易产生毛刺,且易受环境的影响,不利于器件的移植;

在Ubuntu 16.04下,安装petalinux需要的软件包遇到错误,“requested an impossible situation”。安装Ubuntu 16.04时,选择的地区是上海。据说选择香港不会有这个问题。

本实验基于xilinx ARTIX-7芯片验证实现,有时间有兴趣的朋友可在其他FPGA芯片上实现验证。

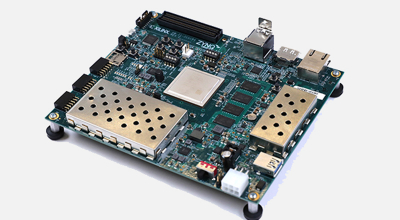

连载[第三篇]讲过,要设计一块接口板和Xilinx官方开发板ZCU104对接来做验证。接口板有两块,分别是相机板和扩展板,相机板搭载Sony IMX172/117传感器;接口板包括FMC插座、万兆以太网SFP+接口、千兆以太网PHY接口和若干引出的IO(可用作MIPI DSI、LVDS显示屏)等

RAM可以通过以下方式初始化:

1,在HDL源代码中指定RAM初始内容;

2,在外部数据文件中指定RAM初始内容。

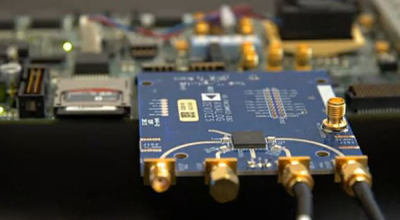

我们处在一个由数字计算机控制的模拟世界里。因此,物联网 (IoT) 设备的设计人员需要将模拟值高效地转换为采样数字表示。答案看似简单,使用一个前置的模数转换器 (ADC) 便能解决问题,然后 ADC 并非千篇一律。因此,设计人员需要了解各种拓扑,以及它们与应用的对应关系。

首先对于纯组合逻辑电路来说,其逻辑功能块的输出仅仅与当前的输入值有关系,其电路延时分析也非常的简单,只考虑输入到输出的信号延时Tdelay,但是影响Tdelay时间的因素比较多,比如不同的器件输入到输出的延时时间不同,不同的工艺条件以及在不同的环境下,Tdelay的时间也不同

VHDL 的一个强大功能是用库来组织 RTL 的不同部分。 通过使用库,不同的设计人员可以做这个工程中自己负责的那部分工作,而不必担心会在命名方面与其他设计师发生冲突。在例化期间,这可以通过手动指定要使用的库或者通过配置语句来完成。

微处理器、FPGA、DSP、模数转换器 (ADC) 和片上系统 (SoC) 器件一般需要多个电压轨才能运行。为防止出现锁定、总线争用问题和高涌流,设计人员需要按特定顺序启动和关断这些电源轨。此过程称为电源时序控制或电源定序,目前有许多解决方案可以有效实现定序