RGMII接口调试使用VIO读取PHY寄存器值

judy 在 周五, 07/05/2019 - 14:05 提交

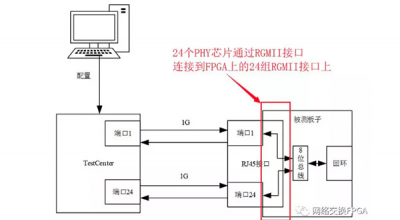

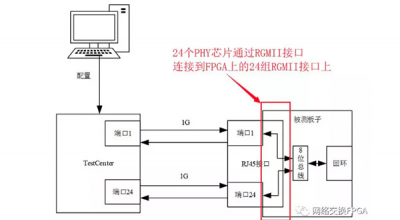

实验室回来一批板子,上面有RGMII接口、SGMII接口等各种接口,怎么测试这些网口是否正常呢?的确需要一些经验。比如RGMII接口,最重要的是看在哪里去做的时钟和数据偏移。这时,常常需要使用VIO去读取PHY里面对应寄存器的值,看是否工作在正常RGMII接口时序模式。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

实验室回来一批板子,上面有RGMII接口、SGMII接口等各种接口,怎么测试这些网口是否正常呢?的确需要一些经验。比如RGMII接口,最重要的是看在哪里去做的时钟和数据偏移。这时,常常需要使用VIO去读取PHY里面对应寄存器的值,看是否工作在正常RGMII接口时序模式。

此博客面向想要开始使用 PetaLinux、了解其关键工具、概念和功能的任何人。在第一篇博客文章中,我们将介绍如何针对 ZCU102 开发板创建 PetaLinux 工程,以及如何修改镜像

根据美国土木工程师学会(ASCE)发布的2017年基础设施报告卡,美国614,387座桥梁中近40%至少有半个世纪的历史。2016年,近10%的车辆在结构上存在缺陷。平均每天有1.88亿辆车跨越结构上不足的桥梁。桥梁的管理者们不断寻找更能减小成本效益的方法来保持桥梁的良好维修

技术这个东西,如果只是用在工作岗位上的话,就是一个“搬砖”的工具,如果把它分享出来,没准还能碰撞出有意思的东西来,你们说是吧?好了,这一系列博文教程叫做“FPGA软硬件加速入门”,顾名思义,就是利用FPGA本身的特点,在软硬件进行不同的系统分工,加速系统输出的速度(主要是计算),我会尽量从入门者的角度讲解相关内容

ESIstream是一个开源的串行数据接口协议,成本极低,支持多种FPGA架构的简单硬件实现,并占用最小的资源。简单来说,它是JEDEC的JESD204B子集1和2标准的开源替代方案。另外,ESIstream可为用户带来很多好处,这里将讨论其中的一些,包括低复杂度、低链接延迟和实现确定性延迟的简单方案。

在VCU TRD 2019.1的Linux里,使用devemem读写内存,得到错误“devmem: mmap: Operation not permitted”。

本文从最原始文件搭建仿真环境的思路出发,尝试着研究脱离Vivado单独建仿真环境的过程中都会遇到什么问题,采用什么样的方法比较容易解决,笔者试了好几个工程,总结出一套相对完善的解决思路,来分享给大家。

现代高速模数转换器(ADC)已经实现了射频(RF)信号的直接采样,因而在许多情况下均无需进行混频,同时也提高了系统的灵活性和功能。本系列文章将从三个部分入手,说明如何将散射参数(也称为S参数)应用于直接射频采样结构的设计。

在项目中,CERN研究人员通过将AI推理和性能关键传感器的预处理在部署于大型强子对撞机(LHC)中的Xilinx Virtex Ultrascale FPGA上结合,通过自行设计的一套HLS4ML的软件工具,可定制计算极大的加速了处理能力, 并且使得神经网络推理的延时降低到100ns数量级

该系列前两篇主要扯了扯Linux中GUI相关的DRI框架及相关组件实现方式。细想一下,对于GUI相关的加速能做的其实不多,开发一个2D或3D的显卡加速子模块对于一个DEMO教程的量级来说工作量太大,我们在这只实现一下简单的功能