Pynq框架&Ultra96|FPGA加速N粒子重力并行模拟

judy 在 周五, 06/21/2019 - 10:40 提交

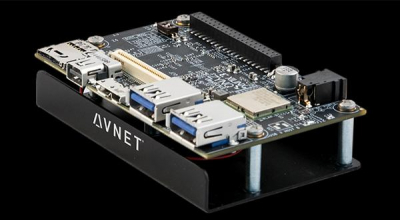

通过使用以200 MHz运行的8个并行浮点加速器,展示小型ZU3EG SoC的科学计算能力。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

通过使用以200 MHz运行的8个并行浮点加速器,展示小型ZU3EG SoC的科学计算能力。

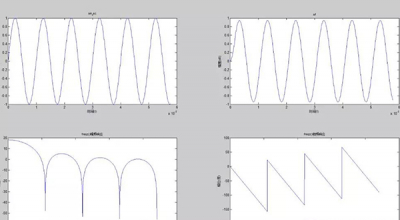

在实现多级CIC滤波器前我们先来了解滑动平均滤波器、微分器、积分器以及梳状滤波器原理。CIC滤波器在通信信号处理中有着重要的应用。

Design Automation Conference 自动设计大会是全球久负盛誉的产学研交流盛会,也是计算机学会推荐的A类会议之一。2019年第56届DAC大会在拉斯维加斯举行,Xilinx将平台升级到了支持Pynq框架的Ultra96,该平台搭载了Xilinx UltraScale+ ZU3器件。

互联网的下半场,科技公司为面对更加严峻的竞争环境,越来越重视开源节流。而对于身处其中且撑起 IT 半边天的技术人,如今如何了?从技术角度来看,其又该作何改变顺应潮流?接下来,我们将从 JetBrains 最新发布的《2019 开发人员生态系统现状》报告中一窥究竟。

在使用 PCI Express IP 进行设计时,如果在第一次尝试与链接伙伴建立链接时就非常顺利,那是非常不错的。但是,有时链接不会那么顺利。成功的 PCI Express 链接是来自两个不同供应商的产品相互兼容的结果。如果链接失败,问题有可能出在任何一方。

近几年SDN之父Nick教授身体力行的开始改造OpenFlow,网络设备第一次和计算设备一样具有了可编程的能力。和OpenFlow刚刚面世一样,用于网络设备编程的P4编程语言也存在众多误解。本文的主要目的就是解惑P4编程语言的几个常见误区。

作者:hankf,Xilinx Employee

Ubuntun 16.04系统,PetaLinux 2019.1 执行"petalinux-config", 失败。

本篇主要以Xilinx的xc7z010 的SOPC(zybo的开发板)为硬件平台,在以下几方面介绍:以zynq 7000的逻辑资源(PL)搭建CRTC/Encoder/Connector硬件模块,以HDMI输出接口为例,介绍各个模块的接口特性;会先给出DRM+KMS驱动框架下的主要模块,并针对上述硬件子模块分析对应的内核驱动部分;

AXI (Advanced eXtensible Interface) 本是由ARM公司提出的一种总线协议, Xilinx从 6 系列的 FPGA 开始对 AXI 总线提供支持,目前使用 AXI4 版本。