Xilinx ZYNQ UltraScale+系列连载[第三篇]写一篇简单需求

judy 在 周四, 05/16/2019 - 11:20 提交

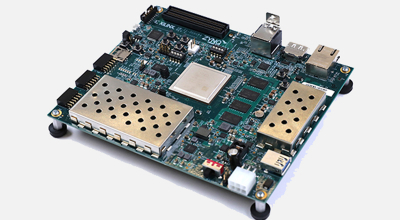

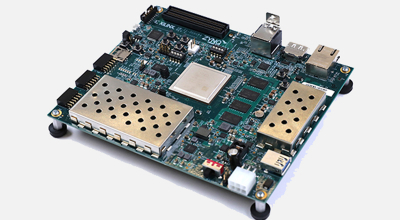

做事情讲究个“谋定而后动”,做研发尤其如此,准备工作一定要做得充分了,需求一定要理解明确了,方可开始吭哧吭哧继续往下干。楼主先准备以ZCU104为平台,实现一个视频处理和传输系统,算是熟悉ZYNQ UltraScale+ MPSoC器件。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

做事情讲究个“谋定而后动”,做研发尤其如此,准备工作一定要做得充分了,需求一定要理解明确了,方可开始吭哧吭哧继续往下干。楼主先准备以ZCU104为平台,实现一个视频处理和传输系统,算是熟悉ZYNQ UltraScale+ MPSoC器件。

修改Xilinx的定时器裸核应用程序(baremetal, standalone)例子xttcps_intr_example.c,可以测量中断响应延迟。然后在单板上运行,以及在XEN的虚拟机上运行,可以分别测量这两种情况下的中断响应延迟。

设备配置包含用于初始化和配置ps和pl的所有方法及过程。在软件控制下,ps内的DevC提供用于初始化和配置ps和pl的手段和方法,在zynq中提供两个模块用于控制配置过程:

1. BootROM,一个静态存储块器块,当上电复位和暖复位后,有Cortex-A9的CPU执行这个内置程序;

随着AI的广泛应用,深度学习已成为当前AI研究和运用的主流方式。面对海量数据的并行运算,AI对于算力的要求不断提升,对硬件的运算速度及功耗提出了更高的要求。目前,除通用CPU外,作为硬件加速的GPU、NPU、FPGA等一些芯片处理器在深度学习的不同应用中发挥着各自的优势,但孰优孰劣?

SDK里带有xttcps_intr_example.c,可以产生时钟中断和PWM方波。MPSoC有四个TTC,总共12个timer。xttcps_intr_example.c缺省使用 12个中的第0个和第1个,TTC0和TTC1。如果修改为其它TTC timer, xttcps_intr_example.c运行出现异常

Xen Dom 0的Linux kernel和文件系统,功能应该越少越好,文件应该越小越好。文件太大,可能引起启动失败。只含有PS的HDF文件,编译出来的rootfs.cpio.gz.u-boot有49MB。经过分析,target文件系统中,/usr/bin占用93MB,其中QEMU的文件占用了92MB.

本文提出一套适用于高压大功率电力电子设备通用型控制控制器。该控制器采用主控制板与其他插件板相分隔的分板块硬件系统结构,结合了DSP、FPGA、CPLD各自性能特点的同时兼顾了通用性;提出了多时间尺度控保融合的软件设计方案,分别从系统级、器件级、信号级三个层面实现对设备的控制和保护

作者:hankf,Xilinx Employee

ZDMA应用例子xzdma_simple_example.c 缺省只运行一次。

要解决任何综合崩溃问题,通常应该从了解崩溃发生在综合的哪个阶段着手,以及工具方面是否有任何迹象指向特定的模块、赋值、声明或推断。如果以下文章无法帮助您解决您查询的问题,请分享在运行文件夹中生成的 hs_pidxxxx.log 文件以及“project_name.runs/synth_1/”目录下的综合日志文件。

存在很多不同的通信协议,这里只列出我们PLC中较常用的协议。下表显示了这些协议之间的一些关键差异,之后对每种协议进行简要说明。