高速FPGA系统设计几条军规

judy 在 周五, 03/29/2019 - 16:03 提交

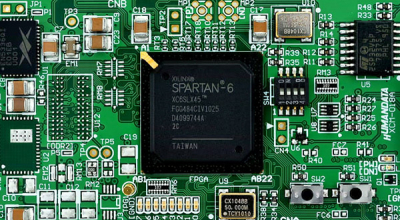

如果符合一些简单的设计原则,采用最新的Xilinx7系列FPGA架构上实现无线通信。Xilinx公司已经创建了典型无线数据路径的设计范例,表明中速级(-2)器件上使用的几乎100%的 slice资源都支持500 MHz以上的时钟频率。如何真正时序高速设计,需要注意一下几点

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

如果符合一些简单的设计原则,采用最新的Xilinx7系列FPGA架构上实现无线通信。Xilinx公司已经创建了典型无线数据路径的设计范例,表明中速级(-2)器件上使用的几乎100%的 slice资源都支持500 MHz以上的时钟频率。如何真正时序高速设计,需要注意一下几点

Alveo 数据中心加速卡在硬件中配置了两个 QSFP 端口。这些如何用于在 U200/U250 卡上启用以太网子系统 IP?

利用卷积神经网络(Convolutional Neural Network, CNN) 等深层神经网络的解决方案,可以逐渐取代基于算法说明的传统图像处理工作。尽管图像预处理、后期处理和信号处理仍采用现有方法进行,但在图像分类应用中(缺陷、对象以及特征分类),深度学习变得愈加重要

FPGA设计的特点是需要不断不断的迭代各个设计流程来达到最终的设计,同时迭代的成本大,它比单片机开发更注重迭代的开发思想。所以,设计的前期一定要从系统的角度考虑好系统的方案,然后在系统这个方案中不断的迭代,不然后期发现由于系统方案的问题就得不偿失了,好的系统架构就是成功一大半了

同步逻辑是时钟之间有固定的因果关系。异步逻辑是各时钟之间没有固定的因果关系。 答案应该与上面问题一致。同步时序逻辑电路的特点:各触发器的时钟端全部连接在一起,并接在系统时钟端,只有当时钟脉冲到来时,电路的状态才能改变

针对CMOS图像传感器采集图像过程中的噪声预处理问题,提出一种在FPGA中实现的可配置的自适应加权均值滤波模块设计方案。该模块通过检测滤波窗口内不同方向的方差来确定纹理方向,从而自动生成相应的加权系数,可以对宽度不超过4 094像素的图像进行流水线式的加权均值滤波处理,达到去噪保边的目的

Vivado是Xilinx公司的FPGA开发工具,熟悉Xilinx的工程师应该对ISE比较不陌生,但是随着时代的发展,FPGA芯片进步很快,Xilinx也已经宣布不再对ISE进行更新,这就意味着Vivado将在以后的发展中逐渐取代ISE,所以掌握好Vivavo的使用,是一个FPGA工程师必备的技能。今天的文章主要是讲解怎么调用Modelsim进行仿真

MPSoC EV 系列支持H.265编解码。在规格中,1080p编解码都可以达到8路1080p30,总体相当于1080p240。使用2018.3 VCU TRD 实际测试,性能更好。按如下测试,编码每路的帧率达到达到45,总体相当于1080p350;解码总体相当于1080p390。编码时,每路的CPU负载在15%左右

据观察,HLS的发展呈现愈演愈烈的趋势,随着Xilinx Vivado HLS的推出,HLS可以在一定程度上降低FPGA的入门门槛(不用编写RTL代码),也可以在某些场合加速设计与验证(例如在FPGA上实现OpenCV函数),但个人还是喜欢直接从RTL入手,这样可以更好的把握硬件结构

【问题描述】:

我的 SD 在 SD1 上,没在 SD0 上,所以我不能从这引导。

怎样才能把 FSBL 交给 SD?

【解决方案】:

SD: