Zynq UltraScale+ RFSoC ZCU111 评估套件 (rev 1.0 EVB) — 运行 TRD 时测量的 VADJ 值与 SCUI GUI 中设置的不同

judy 在 周五, 09/30/2022 - 10:16 提交

对于 ZCU111 rev 1.0 EVB 而言,如果 VADJ 值在 SCUI GUI 中配置为 1.8V(或保留默认值)

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

对于 ZCU111 rev 1.0 EVB 而言,如果 VADJ 值在 SCUI GUI 中配置为 1.8V(或保留默认值)

FPGA广泛应用于各种电子系统,甚至取代ASIC,但其周围具有复杂的电源系统

在硬件设计电路中,根据芯片功能复杂度,可编程芯片一般都需要不止一种供电电源来驱动芯片内部的不同功能块

PetaLinux 是一个强大的实用工具,支持设计人员轻松创建 Linux 镜像并在自己的目标平台上运行。

本篇设计咨询涵盖了 Versal GTM 复位不稳定问题

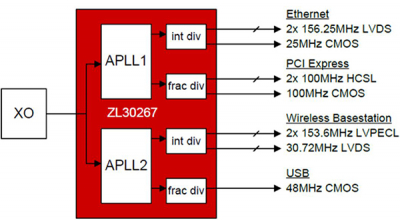

随着FPGA的功能越来越强大,并且有SOC等异构的架构不断演进,硬件设计也有更多的时钟要求

KR260首先从QSPI加载BOOT.BIN启动U-BOOT,U-BOOT再从SD(TF)卡的第1个分区(sda1)启动Linux内核

在较大的逻辑设计中,用于多片FPGA 切割处的互联IO之间的连接,一般通过互联电路板或特制线缆这两种形式进行互联。

在调试时序约束的过程中,用户常常会对除了顶层约束外所涉及的繁杂的时序约束感到困惑而无从下手。

与众多其他行业一样,广播商和内容制作商的工作流也受到了思维模式变化带来的影响