Nested DFX

judy 在 周四, 07/22/2021 - 09:24 提交

了解如何将动态区域放置在动态区域内,以扩展 Dynamic Function eXchange 设计的灵活性和效率。

了解如何将动态区域放置在动态区域内,以扩展 Dynamic Function eXchange 设计的灵活性和效率。

使用 Alveo U30 软件开发者套件 (SDK) 在一天内启动开发。观看视频,快速上手。

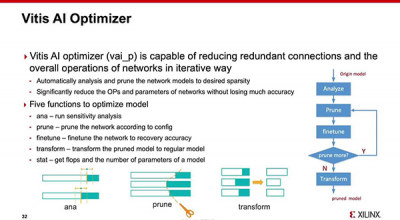

为专用硬件架构设计神经网络,是近年来的热门话题,特别是在边缘器件上。在本次演讲视频中,您将了解如何借助 Once-for-All 神经网络,以低成本形式为 Xilinx 普及型 AI 平台 Vitis AI 搜索和部署高效率模型。

Xilinx 器件及 Vitis/Vitis AI 解决方案可为众多应用加速,包括视频处理、图像预处理、AI 推断以及内存带宽优化等。在本视频中,我们将演示如何使用 Xilinx ZCU104 开发人体检测应用。

Xilinx 推出 Versal™ HBM 系列,在单个平台上融合了高速存储器、安全连接和自适应计算,面向计算最密集、内存受限、高带宽应用。

Versal Premium 通过全新的 GTM SERDES 提供了 112G PAM4。 本视频对此项技术进行了概述, 并演示了 SERDES 运行于直接连接铜缆。

Xilinx 的 16nm FPGA、SoC 和 7nm Versal™ ACAP 以硬化模块及软 IP 形式提供多种架构组件,这使得它们成了设计新一代安全设备的理想之选。这些 IP 包括高速串行解串器和多速率接口 IP,例如硬化 MAC、PCIe® 接口和内存控制器等。

了解块设计容器及其兼容性。

在本视频中,我们展示了在 XCZU47DR 器件的双模块中使用两个 5GSPS ADC 的 10GSPS ADC 性能。

当今的设计突破了器件容量和性能的极限,常常为及时满足设计目标带来艰巨的挑战。了解 UFDM(超快设计方法)的最新发展,这是一系列基于工厂专家经验的最佳实践,在过去几年里他们帮助客户解决了最棘手的设计收敛问题,并获得了最佳结果质量。同时,还可了解非常实用的 Vivado 综合与实现技巧,以提升生产力。