赛灵思硬件开发策略

judy 在 周四, 07/08/2021 - 09:25 提交

软件和 AI 营销副总裁 Ramine Roane 将讨论行业趋势,并带您了解最新的 Xilinx 解决方案和工具。了解 Xilinx 自适应计算如何提高加速应用的标准。

软件和 AI 营销副总裁 Ramine Roane 将讨论行业趋势,并带您了解最新的 Xilinx 解决方案和工具。了解 Xilinx 自适应计算如何提高加速应用的标准。

Xilinx Zynq RFSoC 系列最新成员的视频演示:RFSoC DFE 或数字前端。在视频中,我们将展示在没有 CFR 和 DPD 模块的情况下, Zynq DFE 的 ACLR 和 EVM 性能。

了解 Xilinx 和 Cisco 如何利用 Keysight 的 Open RAN Studio 解决方案来验证具有 CPRI 接口的 [仿真] 传统无线电单元的运行和性能,以及 Xilinx 大规模 MIMO O-RU 参考设计,通过采用 Xilinx 技术的 Cisco 基站路由器共享基于以太网的通用 eCPRI 前传网络,最终将在传统 RU 和 O-RAN DU 之间执行前传网关功能。

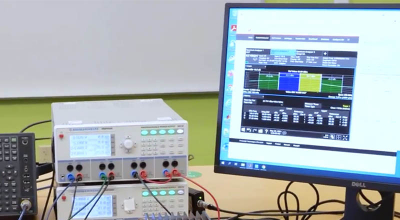

该演示展示了 Xilinx DPD v11 如何管理 GaN PA 的长期存储存应。该演示使用 Wolfspeed 的 39dBm GaN PA,展示了长期存储存应如何影响光谱发射掩模 (SEM) 和误差矢量幅度 (EVM)。看看 DPD v11 全新长期存储管理功能如何纠正这些不足。

本视频简要介绍了 Vitis AI 1.3 工具链,其中包括支持框架的量化器和编译器,并演示了设计流程。

基于 Xilinx Versal 的波束成型解决方案可在 Xilinx 7nm Versal 平台上逐步实现 5G FR1( 7.125GHz 以下)64T64R/32T32R 波束成型解决方案。

了解 Abstract Shell 如何大幅缩短 Dynamic Function eXchange 设计多用户环境的编译时间并增强设计安全性。

了解如何在 2021.1 中大幅简化 IP 版本控制

本期视频邀请到赛灵思高级产品应用工程师陈雯,将介绍 Github 上开源的 Vitis 视频加速库的相关内容,并演示在Avleo U50 的板卡上,从Vitis IDE 中调用Vitis™视觉库的加速内核的应用实例解析。

Xilinx推出具有突破性技术的 Vivado ML 以加速设计收敛并提升 QoR,以及先进的 DFX 功能,可实现时间计算的创新形式。