【视频】在 Alveo 上的 Vitis 加速开发流程(中文)

judy 在 周一, 07/06/2020 - 15:43 提交

欢迎收看本期 Vitis 快速上手视频,我们将重点介绍如何使用 Vitis 在 Alveo 板卡上开发和部署硬件加速应用。Demo 部分会包含 Vitis 图像化界面和命令行流程,并展示如何使用 Xilinx github 加速用例。

欢迎收看本期 Vitis 快速上手视频,我们将重点介绍如何使用 Vitis 在 Alveo 板卡上开发和部署硬件加速应用。Demo 部分会包含 Vitis 图像化界面和命令行流程,并展示如何使用 Xilinx github 加速用例。

基于新型的赛灵思实时服务器( Xilinx RT Server)参考架构,两大全新一体机将双管齐下,助力当今服务提供商以每通道最低成本提供视频质量和比特率优化的多种类型应用。本文我们将开始为您揭开这一与众不同的实时转码一体机...

112G PAM4 是业界通向更高带宽的下一步。该演示主要介绍 Xilinx 针对新一代系统提供 112G 的远景。

本视频演示了如何设置主机以在云或嵌入式器件上开发和运行 Vitis AI 开发环境应用。

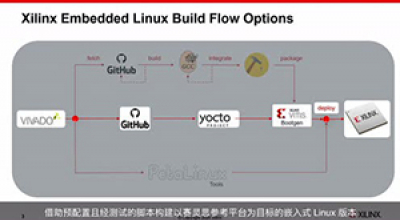

了解嵌入式软件(如 Linux、Xen Hypervisor 和免费实时操作系统)与构建工具(如 Yocto 和 PetaLinux)在 2020.1 发布周期中的新特性。 该视频将详细介绍在该发布周期中所有的新增功能与修改内容

在本视频中我们将简单介绍 PetaLinux 工具开发与构建环境此环境支持客户构建以赛灵思器件为目标的 Linux 版本,并快速评估赛灵思嵌入式平台。

本次网络研讨会概述了 Zynq UltraScale+ RFSoC 及其在有线电视接入远程 PHY 节点中的应用。我们将首先为世界上唯一集成模数转换器的硬件可编程片上系统提供技术概览,并提供关键性能指标。随后,我们将讨论其在远程 PHY 节点上的应用,该节点利用 Xilinx 合作伙伴 Calian SED 提供的关键 IP 块。

本次网络研讨会描述了两个使用 Zynq UltraScale + RFSoC 进行无线通信的设计示例。 首先,让我们回顾一下针对大规模 MIMO(64x64),100MHz LTE(ORAN 7.2 split)的设计,并解释其实现和选型性能数据。

Xilinx 提供了一个基于命令行的自包含实用程序,称为 xclbinutil。 您可以将其用于 Xilinx 加速器二进制容器文件(.XCLBIN)。本视频将带您了解使用 xbutil 检查、报告并修改 xclbin 内容的基本步骤。

本视频解读 DFX 布局规划基本信息视频,介绍了扩展布线区域的使用。这项 Vivado 功能面向 UltraScale 和 Ultrascale+ 器件,可改善 DFX 设计结果,设计人员创建其布局规划时应考量如何运用此功能