PYNQ软件框架研讨会视频回顾

judy 在 周二, 03/31/2020 - 09:29 提交

基于PYNQ软件框架,你只需要了解Python,就可以基于Xilinx可编程SoCs(片上系统)开发自己的可重构嵌入式系统,而不必精通Verilog等硬件设计语言。PYNQ是一个开源软件框架,通过基于浏览器的开发环境和Python语言,使可编程SoC更易于使用,也更便于新的开发者上手使用

基于PYNQ软件框架,你只需要了解Python,就可以基于Xilinx可编程SoCs(片上系统)开发自己的可重构嵌入式系统,而不必精通Verilog等硬件设计语言。PYNQ是一个开源软件框架,通过基于浏览器的开发环境和Python语言,使可编程SoC更易于使用,也更便于新的开发者上手使用

通过视频简要了解整个 Xilinx 嵌入式处理产品组合中 Xilinx嵌入式软件堆栈中的组件。

自定义 RTL Verilog 代码可以替换 HLS 项目中的 C 函数。 然后,通过 JSON 文件并使用 ap_ctrl_chain 协议将 RTL 编织到其余 C 代码中,以管理 RTL 和 C 代码之间的数据事务。

Zynq® UltraScale+™ RFSoC ZCU216 评估套件配备第三代业界唯一单芯片自适应射频平台,是快速原型设计和 RF 应用开发的理想平台。该视频介绍了 ZCU216 评估套件提供的重要板载组件和配件。

指导 SDK 用户如何将现有 SDK 项目迁移至 Vitis™ 统一软件环境

本视频由 Baicells(佰才邦) 在 2019 MWC 上展示其面向 NR 加速及同步的 O-RAN 和 TIP Open RAN PCIe 加速卡,以及面向 O-RAN 的室内 Radion Hub。

本视频以 Alveo 加速卡为例,教您快速开始使用赛灵思 Vitis 开发软件进行开发。

在本视频教程中,您将了解 Aveo 加速卡的 Vitis 基本流程,以及如何使用 Vitis 分析仪分析编译结果。

如果您想开发面向最先进技术和协议的下一代最快速、最安全的网络,请跟随 Xilinx 高级产品线经理 Mike Thompson,了解 Versal ACAP 器件中的集成功能

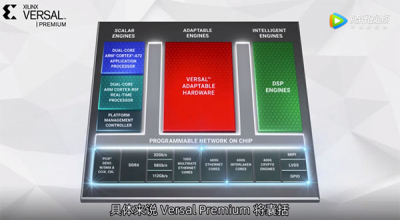

本视频由赛灵思公司 SerDes 系统工程和应用高级总监 Chris Borrelli 向您详细介绍 Versal Premium 系列的技术特性。