【ZYNQ Ultrascale+ MPSOC FPGA教程】第四章 PL的LED实验

judy 在 周五, 12/25/2020 - 09:56 提交

在本例程中,我们要做的是LED灯控制实验,每秒钟控制开发板上的LED灯翻转一次,实现亮、灭、亮、灭的控制。会控制LED灯,其它外设也慢慢就会了。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

在本例程中,我们要做的是LED灯控制实验,每秒钟控制开发板上的LED灯翻转一次,实现亮、灭、亮、灭的控制。会控制LED灯,其它外设也慢慢就会了。

用过Matlab的同学应该都知道,Matlab的慢是出了名的,但是再慢也有优化的方式,下面我们给出几个Matlab编程中常用的优化技巧。

很多初学者看到板上只有一个25Mhz时钟输入的时候都产生疑惑,时钟怎么是25Mhz?如果要工作在100Mhz、150Mhz怎么办?其实在很多FPGA芯片内部都集成了PLL,其他厂商可能不叫PLL,但是也有类似的功能模块,通过PLL可以倍频分频,产生其他很多时钟。本实验通过调用PLL IP core来学习PLL的使用、vivado的IP core使用方法。

为 VCU129 开发板提供的 BOARDUI.exe 可用于为板载 Si5348 时钟模块编写程序。默认频率为 156.25Mhz,该频率的设置文件在 BOARDUI 的 clockFiles 目录下提供。如何修改时钟频率?

本文主要介绍verilog基础模块,夯实基础,对深入学习FPGA会有很大帮助。

TVM主要的编译过程如下图:Import:将tensorflow,onnx,pytorch等构建的深度学习模型导入,转化成TVM的中间层表示IR。Lower:将高层IR表示转化成低阶TIR表示。Codegen:内存分配和硬件可执行程序生成。

NeoPixels是数字控制的红、绿、蓝像素。由于每种颜色都由8位表示,总共24位,因此每个像素可以显示16777216种颜色中的一种。每个NeoPixel实际上是一个WS2812 LED。这些LED包含五个输入端,相对于地(VSS)在3.3V到5.0V(VDD和VCC)的电压范围内工作。

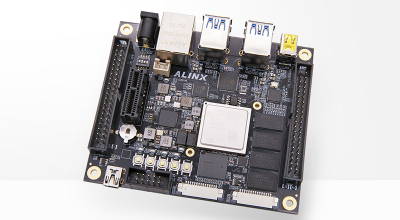

AXU2CGA/B的特点是体积小并扩展了丰富的外设。主芯片采用Xilinx公司的Zynq UltraScale+ MPSoCs CG系列的芯片,型号为XCZU2CG-1SFVC784I。AXU2CGA的PS端挂载了2片DDR4(2GB,32bit)和1片256Mb的QSPI FLASH。

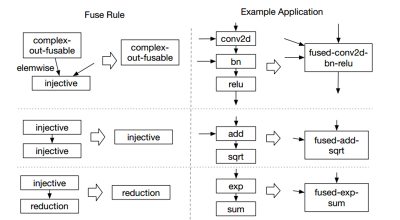

算符融合将多个计算单元揉进一个计算核中进行,减少了中间数据的搬移,节省了计算时间。TVM中将计算算符分成四种:

1 injective。一一映射函数,比如加法,点乘等。

2 reduction。输入到输出具有降维性质的,比如sum。

3 complex-out。这是计算比较复杂的,比如卷积运算等。

4 opaque。无法被融合的算符,比如sort。

Zynq UltraScale+ MPSoC系列是Xilinx第二代Zynq平台。其亮点在于FPGA里包含了完整的ARM处理子系统(PS),包含了四核Cortex-A53处理器或双核Cortex-A53加双核Cortex-R5处理器,整个处理器的搭建都以处理器为中心,而且处理器子系统中集成了内存控制器和大量的外设,使处理器核在Zynq中完全独立于可编程逻辑单元