高层次综合技术原理浅析

judy 在 周四, 12/31/2020 - 14:13 提交

说起高层次综合技术(High-level synthesis)的概念,现在有很多初学者简单地把它理解为可以自动把c/c++之类地高级语言直接转换成底层硬件描述语言(RTL)的技术。其实更准确的表述是:由更高抽象度的行为描述生产电路的技术。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

说起高层次综合技术(High-level synthesis)的概念,现在有很多初学者简单地把它理解为可以自动把c/c++之类地高级语言直接转换成底层硬件描述语言(RTL)的技术。其实更准确的表述是:由更高抽象度的行为描述生产电路的技术。

FIFO是FPGA应用当中非常重要的模块,广泛用于数据的缓存,跨时钟域数据处理等。学好FIFO是FPGA的关键,灵活运用好FIFO是一个FPGA工程师必备的技能。本章主要介绍利用XILINX提供的FIFO IP进行读写测试。

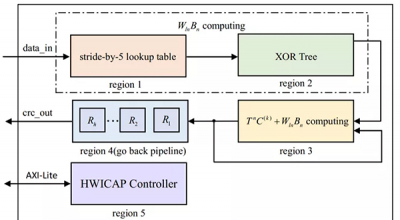

循环冗余码校验(CRC)是一种众所周知的错误检测代码,已广泛用于以太网,PCIe和其他传输协议中。现有的基于FPGA的实现解决方案在高性能场景中会遇到资源过度利用的问题。填充零问题和可编程性的引入进一步加剧了这个问题。在本文中,提出了stride-by-5算法,以实现FPGA资源的最佳利用。提出了pipelining go back算法来解决填充零问题。

FPGA本身是SRAM架构的,断电之后,程序就消失,那么如何利用FPGA实现一个ROM呢,我们可以利用FPGA内部的RAM资源实现ROM,但不是真正意义上的ROM,而是每次上电都会把初始化的值先写入RAM。本实验将为大家介绍如何使用FPGA内部的ROM以及程序对该ROM的数据读操作。

DONE 变为高电平后应给 CCLK 应用多少个时钟周期以确保我的 FPGA 器件完全工作。

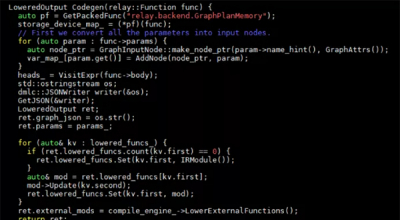

接着上一章继续深入代码,在BuildRelay中会调用Codegen函数。这个函数实现在src/relay/backend/graph_runtime_codegen.cc中。Codegen实现了内存的分配,IR节点到TIR节点的转换,tir图节点的一个调度优化。

Zynq UltraScale+ MPSoC VCU DDR 控制器是一款专用 DDR 控制器,只支持在 Zynq UltraScale+ MPSoC EV 部件上与 Zynq UltraScale+ MPSoC VCU(H.264/H.265 视频编解码器)连用。

因此,调试将不同于 MIG 等传统 Xilinx DDR 控制器。

RAM是FPGA中常用的基础模块,可广泛用于缓存数据的情况,同样它也是ROM,FIFO的基础。本实验将为大家介绍如何使用FPGA内部的RAM以及程序对该RAM的数据读写操作。

赛灵思 MATLAB & Simulink Add-on插件是将 ModelComposer 和 System Generator forDSP 完美结合的统一工具。它是一种基于模型的设计工具,帮助算法和 RTL /硬件开发者在 MathWorks Simulink® 环境中以赛灵思器件为目标,快速开展设计与探索。

使用 2018.2 Ultra96 PetaLinux BSP 构建图像时,如果我在 Matchbox 桌面点击关断图标,电路板不关断。服务器窗口会关闭,屏幕变为空白,但电路板还在运行。