开发者分享 | PS IIC 和 AXI IIC 调试技巧

judy 在 周一, 01/25/2021 - 15:39 提交

“IIC 协议与编程序列” 一文,我们为内部集成电路 (IIC) 协议的初学者们提供了有关该协议基础知识和编程序列的详细解释。在本篇博文中,我们将探讨有关 AXI IIC 和 PS IIC 的自调试技巧。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

“IIC 协议与编程序列” 一文,我们为内部集成电路 (IIC) 协议的初学者们提供了有关该协议基础知识和编程序列的详细解释。在本篇博文中,我们将探讨有关 AXI IIC 和 PS IIC 的自调试技巧。

用了几章的篇幅写了一些粗读TVM代码的收获,虽然读了一点皮毛,但是还是掌握了TVM的基本架构和代码组成,算是给以后的精读打下了一点基础吧。从这章开始再从头捋一遍TVM代码,顺序是frontend-build-optimize-lower-target

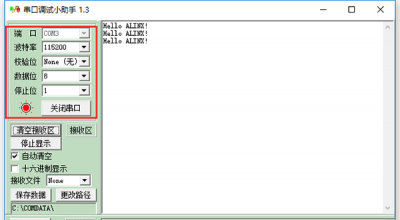

在前面的实验中,大家或多或少会发现有打印信息的情况,主要是调用”xil_printf”或”printf”,但是通过什么打印信息呢?我们还记得打印信息之前设置了串口,是的,确实是串口,但这些函数是如何调用串口呢?其实我们可以在”xil_printf”函数定义中看到,注意outbyte函数就是调用UART打印的

实时时钟(rtc)单元为系统和应用软件提供精确的时间基准。为了满足高精度的需要,实时时钟还包括校准电路,以补偿温度和电压波动。RTC 由 VCC-PSAUX 或 VCC-PSBATT 电源供电。当辅助电源可用时,RTC 使用它保持计数器活动。当辅助电源不可用时,RTC 自动切换到 VCC PSBATT 电源。

此文基于第十八章内容进行软件开发

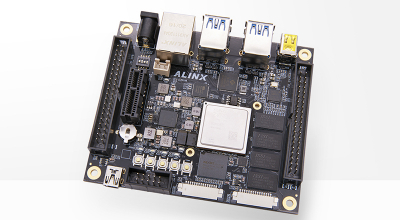

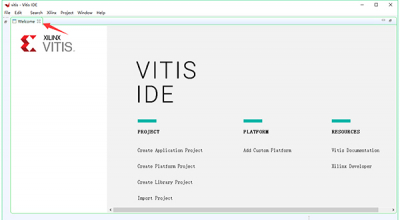

前面的实验都是在PL端进行的,可以看到和普通FPGA开发流程没有任何区别,ZYNQ的主要优势就是FPGA和ARM的合理结合,这对开发人员提出了更高的要求。从本章开始,我们开始使用ARM,也就是我们说的PS,本章我们使用一个简单的串口打印来体验一下Vivado Vitis和PS端的特性。

为满足合成孔径雷达实时成像、数据回放等高速可靠数据传输需求,解决传统数据传输系统由于接口要求高、体积与功耗大以及网络配置不灵活等原因不适合用于外场试验的问题,基于 ZYNQ 芯片设计一种光纤接口到以太网接口的数据传输系统。主要介绍数据传输流程的实现方法,并提出一种三级乒乓和指令并行的优化策略保证数据正确,提高传输速度

所有的工程目录下都有个bootimage文件夹,存放了对应的BOOT.bin文件,可将此文件拷贝到Vitis_image_download文件夹,覆盖原有的BOOT.bin。也可以把BOOT.bin放到SD卡启动验证功能

基于HDMI输出实验,本章介绍7寸液晶屏的显示。LCD屏显示方式从屏幕左上角一点开始,从左向右逐点显示,每显示完一行,再回到屏幕的左边下一行的起始位置,在这期间,需要对行进行消隐,每行结束时,用行同步信号进行同步

在本文中,我们将重点放在如何能够在不需要特殊的库或类的情况下修改代码风格以实现C代码实现并行性。Xilinx HLS 编译器的显着特征是能够将任务级别的并行性和流水线与可寻址的存储器 PIPO或 FIFO相结合。