开发者分享 | 如何使用 10G/25G 以太网 IP core 上的 1588 功能

judy 在 周四, 04/01/2021 - 11:39 提交

以太网 IP 核的 1588 功能是用来实现,在 IP 内部为TX侧发送包打上发送出去这个时间节点的时间戳,以及获得 RX 侧收回来的包在 IP 接口处的时间戳。然而10G/25G 的 IP 例子工程没有提供演示,本文主要介绍了如何使用这个 IP 的 1588功能。

为智能硬件开发者、创客提供有关基于英特尔嵌入式处理器的应用技术介绍和合作伙伴方案介绍

以太网 IP 核的 1588 功能是用来实现,在 IP 内部为TX侧发送包打上发送出去这个时间节点的时间戳,以及获得 RX 侧收回来的包在 IP 接口处的时间戳。然而10G/25G 的 IP 例子工程没有提供演示,本文主要介绍了如何使用这个 IP 的 1588功能。

因为 BD 中连线太多,所以想自定义下 interface 简化连线,定义好了一个 interface,但当准备在自定义 IP 中指定它时,发现我把一个信号的方向搞错了,应该定义成 out,但实际定义成了 in,所以想简单的改一下方向。

Alveo 加速卡除了有我们 ultrascale+系列的芯片以外,还有 TI 的 MSP432,它的作用就是监控板子的状态,比如电流电压温度等信息。主控端可以通过 FPGA,访问 MPS432,然后获取这些信息。那么怎么样简单的获得这些信息呢,为此我们准备了 CMSIP。

从 NAND 闪存启动 Zynq-7000 SoC 器件时,BootROM 中的 NAND 驱动在 NAND 参数页面 (Parameter Page) 中执行读取时不会对输入进行验证。如果从参数页面读入的备用字节包含恶意的非法值,则会导致缓冲器上溢,从而可能导致执行任意代码。

Pass是TVM中基于relay IR进行的优化,目的是去除冗余算子,进行硬件友好的算子转换,最终能够提高硬件运行效率。由tensorflow等深度学习框架生成的图机构中,含有很多可以优化的算子,比如expand_dim,len等,其实在编译阶段完全可以优化掉,从而能够减少硬件的计算,以及避免出现硬件不支持的算子。

今天邀请到赛灵思专家和大家分享下如何在 Petalinux 下定位 decice-tree 错误的一些技巧。

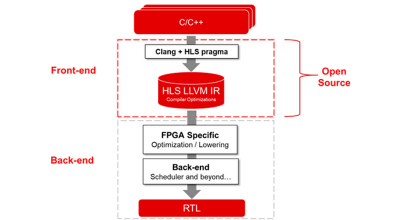

赛灵思一直致力于支持开源计划的不断飞跃,为帮助开发人员和研发社区充分发挥自适应计算的优势,我们再次做出了令人振奋的举措: 在 GitHub 上开放提供 Vitis HLS(高层次综合)前端。Vitis HLS 工具能够将 C++ 和 OpenCL™ 功能部署到器件的逻辑结构和 RAM/DSP 块上。

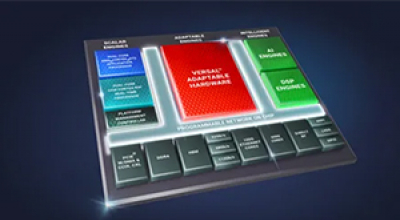

身处智能时代,科技发展日新月异,伴随数据中心、有线网络、5G 无线和汽车等愈加丰富的场景,相应的技术与功能也正经历飞速迭代,因此,单一计算架构已难以应对海量数据处理需求,赛灵思 Versal ACAP多核异构计算平台致力于帮助所有开发者保持即时的灵活应变能力。

目前ASIC的设计变得越来越大,越来越复杂,单片FPGA已不能满足原型验证要求,多片FPGA验证应运而生。RTL逻辑的分割、多片FPGA之间的互联拓扑结构、I/O分配、高速接口都对应用FPGA原型验证的芯片开发者提出了更高的要求也带来了前所未有的挑战。

本文针对上海证券交易所的行情发布系统,采用Verilog硬件描述语言,在FPGA加速卡上开发了对行情信息流的以太网,IP和UDP以及FAST协议的硬件解码,设计了支持指令集编程的微指令加速引擎。与传统的基于软件的方法相比,本文提出的专用硬件处理方案延时可降低10倍以上。